Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- GENERAL DESCRIPTION

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- REVISION HISTORY

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- TERMINOLOGY

- EQUIVALENT INPUT/OUTPUT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- SYSTEM OVERVIEW

- SERIAL INTERFACE TIMING

- COMPLETE REGISTER LISTING

- PRECISION TIMING HIGH SPEED TIMING GENERATION

- HORIZONTAL CLAMPING AND BLANKING

- GENERATING SPECIAL HBLK PATTERNS

- POWER-UP PROCEDURE

- ANALOG FRONT END DESCRIPTION AND OPERATION

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9949

Rev. B | Page 5 of 36

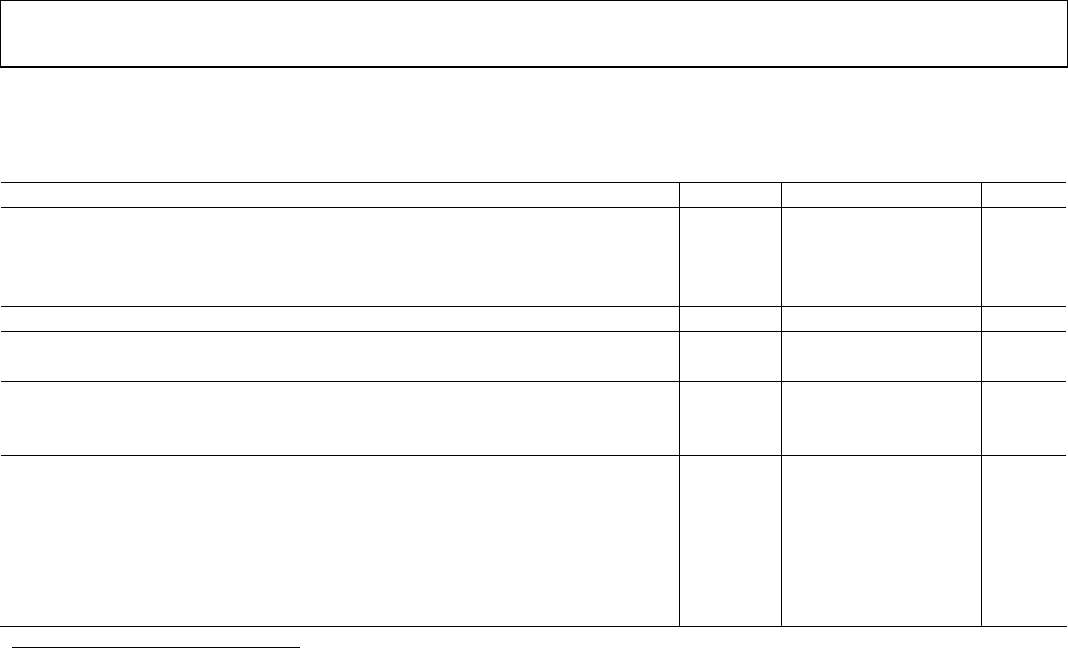

TIMING SPECIFICATIONS

C

L

= 20 pF, f

CLI

= 36 MHz, unless otherwise noted.

Table 4.

Parameter Symbol Min Typ Max Unit

MASTER CLOCK (CLI) (See Figure 16)

CLI Clock Period t

CLI

27.8 ns

CLI High/Low Pulse Width t

ADC

11.2 13.9 16.6 ns

Delay from CLI to Internal Pixel Period Position t

CLIDLY

6 ns

CLPOB PULSE WIDTH (PROGRAMMABLE)

1

t

COB

2 20 Pixels

SAMPLE CLOCKS (See Figure 18)

SHP Rising Edge to SHD Rising Edge t

S1

12.5 13.9 ns

DATA OUTPUTS (See Figure 19 and Figure 20)

Output Delay From Programmed Edge t

OD

6 ns

Pipeline Delay 11 Cycles

SERIAL INTERFACE (SERIAL TIMING SHOWN IN Figure 14 and Figure 15)

Maximum SCK Frequency f

SCLK

10 MHz

SL to SCK Setup Time t

LS

10 ns

SCK to SL Hold Time t

LH

10 ns

SDATA Valid to SCK Rising Edge Setup t

DS

10 ns

SCK Falling Edge to SDATA Valid Hold t

DH

10 ns

SCK Falling Edge to SDATA Valid Read t

DV

10 ns

1

Minimum CLPOB pulse width is for functional operation only. Wider typical pulses are recommended to achieve low noise clamp reference.