Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- GENERAL DESCRIPTION

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- REVISION HISTORY

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- TERMINOLOGY

- EQUIVALENT INPUT/OUTPUT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- SYSTEM OVERVIEW

- SERIAL INTERFACE TIMING

- COMPLETE REGISTER LISTING

- PRECISION TIMING HIGH SPEED TIMING GENERATION

- HORIZONTAL CLAMPING AND BLANKING

- GENERATING SPECIAL HBLK PATTERNS

- POWER-UP PROCEDURE

- ANALOG FRONT END DESCRIPTION AND OPERATION

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9949

Rev. B | Page 32 of 36

V

H

USE SEQUENCE 2

USE SEQUENCE 3

SEQUENCE 2 (OPTIONAL)

HORIZONTAL CCD REGISTER

EFFECTIVE IMAGE AREA

2

8 DUMMY PIXELS

48 OB PIXELS

4 OB PIXELS

10 VERTICAL OB LINES

2 VERTICAL OB LINES

03751-044

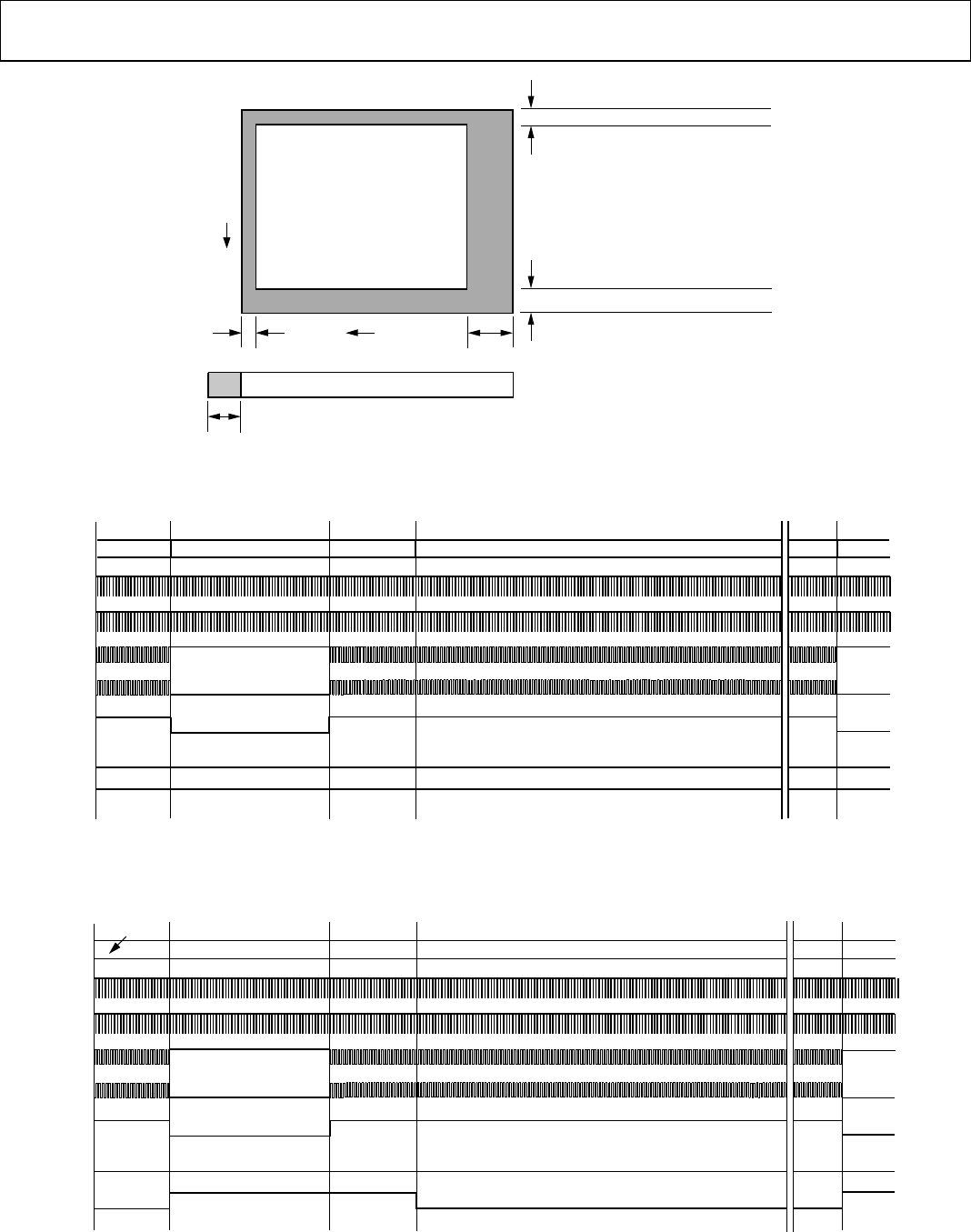

Figure 43. Example CCD Configuration

VERTICAL SHIFT

VERT SHIFT

SEQUENCE 1: VERTICAL BLANKING

CCDIN

SHP

SHD

H1/H3

H2/H4

HBLK

PBLK

CLPOB

DUMMY INVALID PIXELSINVALID PIX

03751-045

Figure 44. Horizontal Sequence During Vertical Blanking

VERTICAL SHIFT

VERT SHIFT

SEQUENCE 2: VERTICAL OPTICAL BLACK LINES

CCDIN

SHP

SHD

H1/H3

H2/H4

HBLK

PBLK

CLPOB

OPTICAL

BLACK

DUMMY

OPTICAL BLACK

03751-046

Figure 45. Horizontal Sequences During Vertical Optical Black Pixels