Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- GENERAL DESCRIPTION

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- REVISION HISTORY

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- TERMINOLOGY

- EQUIVALENT INPUT/OUTPUT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- SYSTEM OVERVIEW

- SERIAL INTERFACE TIMING

- COMPLETE REGISTER LISTING

- PRECISION TIMING HIGH SPEED TIMING GENERATION

- HORIZONTAL CLAMPING AND BLANKING

- GENERATING SPECIAL HBLK PATTERNS

- POWER-UP PROCEDURE

- ANALOG FRONT END DESCRIPTION AND OPERATION

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9949

Rev. B | Page 24 of 36

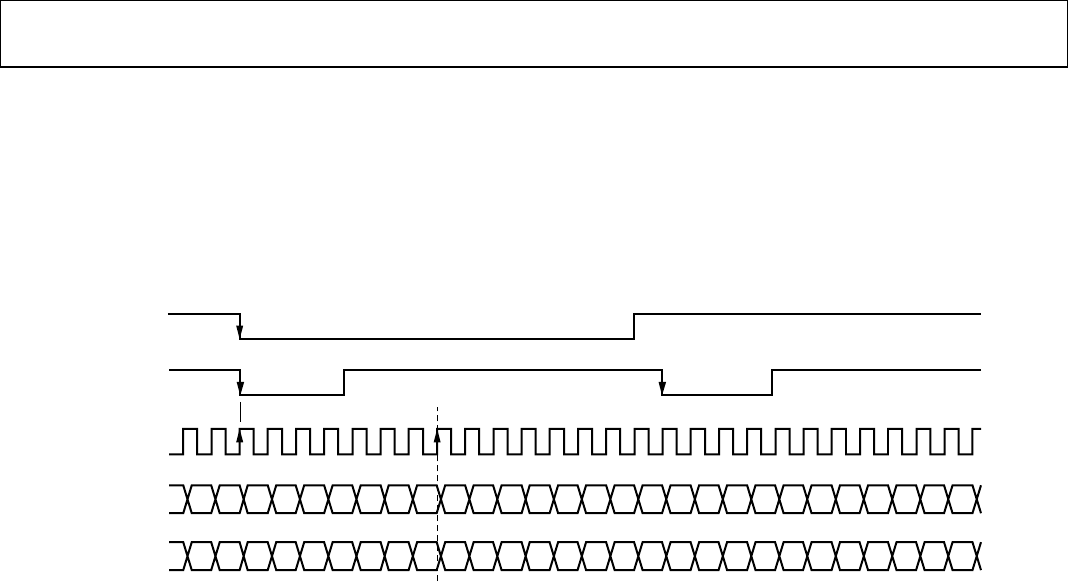

H-COUNTER SYNCHRONIZATION

The H-Counter reset occurs seven CLI cycles following the HD falling edge. The PxGA steering is synchronized with the reset of the

internal H-Counter (see Figure 26).

As mentioned in the H-Counter Behavior section, the AD9949 H-counter rolls over to zero and continues counting when the maximum

counter length is exceeded. The newer AD9949A product does not roll over but holds at its maximum value until the next HD rising edge

occurs.

000 1 12111 0 031100

012345678910111214150123

02

H-COUNTER

RESET

VD

NOTES

1. INTERNAL H-COUNTER IS RESET 7 CLI CYCLES AFTER THE HD FALLING EDGE (WHEN USING VDHDEDGE = 0).

2. TYPICAL TIMING RELATIONSHIP: CLI RISING EDGE IS COINCIDENT WITH HD FALLING EDGE.

3. PxGA STEERING IS SYNCRONIZED WITH THE RESET OF THE INTERNAL H-COUNTER (MOSAIC SEPARATE MODE IS SHOWN).

HD

XXXXXXX

PxGA GAIN

REGISTER

CLI

3

XXXXXXX

H-COUNTER

(PIXEL COUNTER)

X

X

X

X

X

X

03751-027

Figure 26. H-Counter Synchronization