Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- GENERAL DESCRIPTION

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- REVISION HISTORY

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- TERMINOLOGY

- EQUIVALENT INPUT/OUTPUT CIRCUITS

- TYPICAL PERFORMANCE CHARACTERISTICS

- SYSTEM OVERVIEW

- SERIAL INTERFACE TIMING

- COMPLETE REGISTER LISTING

- PRECISION TIMING HIGH SPEED TIMING GENERATION

- HORIZONTAL CLAMPING AND BLANKING

- GENERATING SPECIAL HBLK PATTERNS

- POWER-UP PROCEDURE

- ANALOG FRONT END DESCRIPTION AND OPERATION

- APPLICATIONS INFORMATION

- OUTLINE DIMENSIONS

AD9949

Rev. B | Page 20 of 36

NOTES

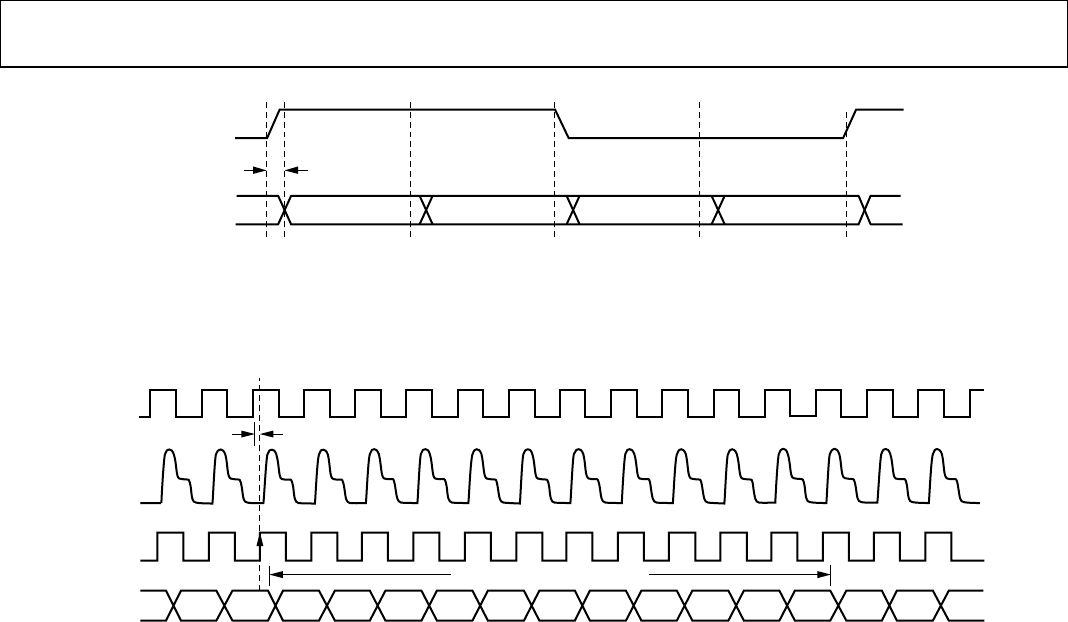

1. DIGITAL OUTPUT DATA (DOUT) PHASE IS ADJUSTABLE WITH RESPECT TO THE PIXEL PERIOD.

2. WITHIN ONE CLOCK PERIOD, THE DATA TRANSITION CAN BE PROGRAMMED TO ANY OF THE 48 LOCATIONS.

P[0] P[48] = P[0]

CLI

1 PIXEL PERIOD

P[12] P[24] P[36]

DOUT

t

OD

03751-020

Figure 19. Digital Output Phase Adjustment

NOTES

1. DEFAULT TIMING VALUES ARE SHOWN: SHDLOC = 0, DOUT PHASE = 0.

2. HIGHER VALUES OF SHD AND/OR DOUTPHASE WILL SHIFT DOUT TRANSITION TO THE RIGHT, WITH RESPECT TO CLI LOCATION.

DOUT

CCDIN

CLI

SHD

(INTERNAL)

N N + 1 N + 2 N + 12N + 11N + 10N + 9N + 8N + 7N + 6N + 5N + 4N + 3 N + 13

N – 13

N– 3N– 4N– 5N– 6N– 7N– 8N– 9N – 10N – 11

N – 12

N– 2

N– 1

N + 1

N

SAMPLE PIXEL N

N– 1

03751-021

t

CLIDLY

PIPELINE LATENCY = 11 CYCLES

Figure 20. Pipeline Delay for Digital Data Output