Datasheet

Table Of Contents

- Features

- Applications

- Functional Block Diagram

- General Description

- Revision History

- Specifications

- Absolute Maximum Ratings

- Pin Configuration and Function Descriptions

- Typical Performance Characteristics

- Test Circuits

- I2C Interface

- Theory of Operation

- Programming the Variable Resistor

- Programming the Potentiometer Divider

- I2C-Compatible 2-Wire Serial Bus

- Level Shifting for Bidirectional Interface

- ESD Protection

- Terminal Voltage Operating Range

- Maximum Operating Current

- Power-Up Sequence

- Layout and Power Supply Bypassing

- Constant Bias to Retain Resistance Setting

- Outline Dimensions

Data Sheet AD5247

Rev. F | Page 13 of 20

I

2

C INTERFACE

The following abbreviations are used in this section:

• S = start condition

• P = stop condition

• A = acknowledge

• X = don’t care

•

W

= write

• R = read

• A6, A5, A4, A3, A2, A1, A0 = address bits

• D6, D5, D4, D3, D2, D1, D0 = data bits

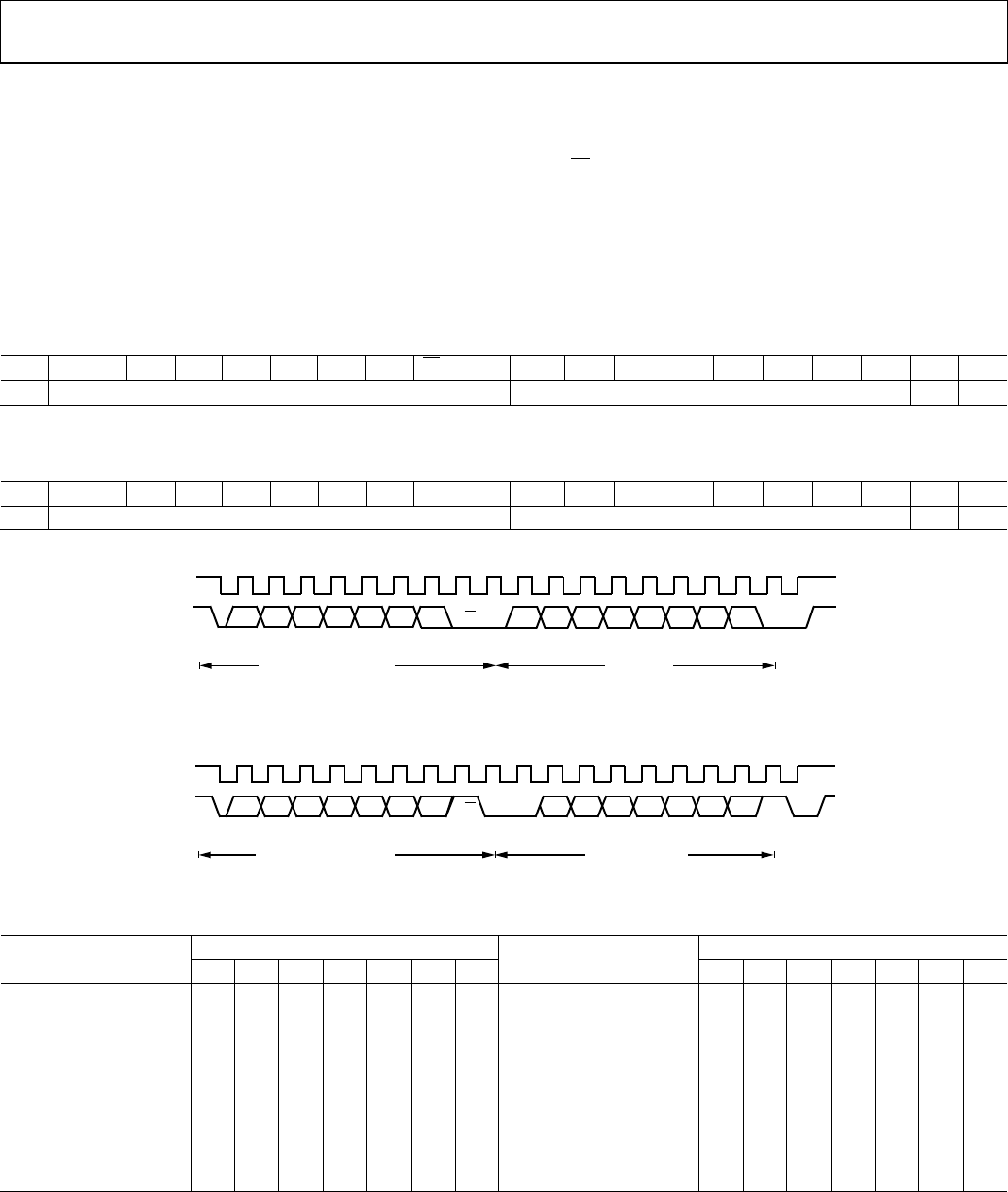

Table 6. Write Mode

S A6 A5 A4 A3 A2 A1 A0

W

A X D6 D5 D4 D3 D2 D1 D0 A P

Slave Address Byte Data Byte

Table 7. Read Mode

S A6 A5 A4 A3 A2 A1 A0 R A 0 D6 D5 D4 D3 D2 D1 D0 A P

Slave Address Byte Data Byte

SCL

FRAME 1

SLAVE ADDRESS BYTE

FRAME 2

DATA BYTE

START BY

MASTER

ACK BY

AD5247

STOP BY

MASTER

SDA

R/W

X D6 D4 D3 D2 D1 D0

1

1

9

ACK BY

AD5247

19

D5

03876-032

A6 A4 A3 A2 A1 A0

ACK

A5

Figure 33. Writing to the RDAC Register

SCL

FRAME 1

SLAVE ADDRESS BYTE

FRAME 2

RDAC REGISTER

START BY

MASTER

ACK BY

AD5247

STOP BY

MASTER

S

R/W

0 D6 D4 D3 D2 D1 D0

11 9

NO ACK BY

MASTER

9

D5

03876-033

A6 A4 A3 A2 A1 A0

A5

Figure 34. Reading from the RDAC Register

Table 8. I

2

C Slave Addresses

Model

Slave Addresses

Model

Slave Address

A6 A5 A4 A3 A2 A1 A0 A6 A5 A4 A3 A2 A1 A0

AD5247BKS5-R2 0 1 0 1 1 1 0 AD5247BKS50-RL7 0 1 0 1 1 1 0

AD5247BKS5-RL7 0 1 0 1 1 1 0 AD5247BKSZ50-RL7 0 1 0 1 1 1 0

AD5247BKSZ5-RL7 0 1 0 1 1 1 0 AD5247BKS100-R2 0 1 0 1 1 1 0

AD5247BKS10-R2

0

1

0

1

1

1

0

AD5247BKSZ100-R2

0

1

0

1

1

1

0

AD5247BKS10-RL7 0 1 0 1 1 1 0 AD5247BKS100-RL7 0 1 0 1 1 1 0

AD5247BKSZ10-RL7 0 1 0 1 1 1 0 AD5247BKSZ100-RL7 0 1 0 1 1 1 0

AD5247BKSZ10-1RL7 0 0 1 0 1 1 1 AD5247BKSZ100-1RL7 0 0 1 0 1 1 1

AD5247BKSZ10-2RL7 0 0 1 0 1 1 0 AD5247BKSZ100-2RL7 0 0 1 0 1 1 0

AD5247BKS50-R2 0 1 0 1 1 1 0