User guide

Table Of Contents

- Cyclone V Hard IP for PCI Express User Guide

- Contents

- 1. Datasheet

- 2. Getting Started with the Cyclone V Hard IP for PCI Express

- 3. Getting Started with the Avalon-MM Cyclone Hard IP for PCI Express

- Running Qsys

- Customizing the Cyclone VHard IP for PCI Express IP Core

- Adding the Remaining Components to the Qsys System

- Completing the Connections in Qsys

- Specifying Clocks and Interrupts

- Specifying Exported Interfaces

- Specifying Address Assignments

- Simulating the Example Design

- Simulating the Single DWord Design

- Understanding Channel Placement Guidelines

- Adding Synopsis Design Constraints

- Creating a Quartus II Project

- Compiling the Design

- Programming a Device

- 4. Parameter Settings for the Cyclone V Hard IP for PCI Express

- 5. Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

- 6. IP Core Architecture

- Key Interfaces

- Protocol Layers

- Multi-Function Support

- PCI Express Avalon-MM Bridge

- Avalon-MM Bridge TLPs

- Avalon-MM-to-PCI Express Write Requests

- Avalon-MM-to-PCI Express Upstream Read Requests

- PCI Express-to-Avalon-MM Read Completions

- PCI Express-to-Avalon-MM Downstream Write Requests

- PCI Express-to-Avalon-MM Downstream Read Requests

- Avalon-MM-to-PCI Express Read Completions

- PCI Express-to-Avalon-MM Address Translation for Endpoints

- Minimizing BAR Sizes and the PCIe Address Space

- Avalon-MM-to-PCI Express Address Translation Algorithm

- Single DWord Completer Endpoint

- 7. IP Core Interfaces

- Cyclone V Hard IP for PCI Express

- Avalon-MM Hard IP for PCI Express

- Physical Layer Interface Signals

- Test Signals

- 8. Register Descriptions

- Configuration Space Register Content

- Altera-Defined Vendor Specific Extended Capability (VSEC)

- PCI Express Avalon-MM Bridge Control Register Access Content

- Avalon-MM to PCI Express Interrupt Registers

- PCI Express Mailbox Registers

- Avalon-MM-to-PCI Express Address Translation Table

- Root Port TLP Data Registers

- Programming Model for Avalon-MM Root Port

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

- Avalon-MM Mailbox Registers

- Correspondence between Configuration Space Registers and the PCIe Spec 2.1

- 9. Reset and Clocks

- 10. Transaction Layer Protocol (TLP) Details

- 11. Interrupts

- Interrupts for Endpoints Using the Avalon-ST Application Interface

- Interrupts for Root Ports Using the Avalon-ST Interface to the Application Layer

- Interrupts for Endpoints Using the Avalon-MM Interface to the Application Layer

- Interrupts for End Points Using the Avalon-MM Interface with Multiple MSI/MSI-X Support

- 12. Optional Features

- 13. Flow Control

- 14. Error Handling

- 15. Transceiver PHY IP Reconfiguration

- 16. SDC Timing Constraints

- 17. Testbench and Design Example

- Endpoint Testbench

- Root Port Testbench

- Chaining DMA Design Examples

- Test Driver Module

- Root Port Design Example

- Root Port BFM

- BFM Procedures and Functions

- 18. Debugging

- A. Transaction Layer Packet (TLP) Header Formats

- Additional Information

December 2013 Altera Corporation Cyclone V Hard IP for PCI Express

User Guide

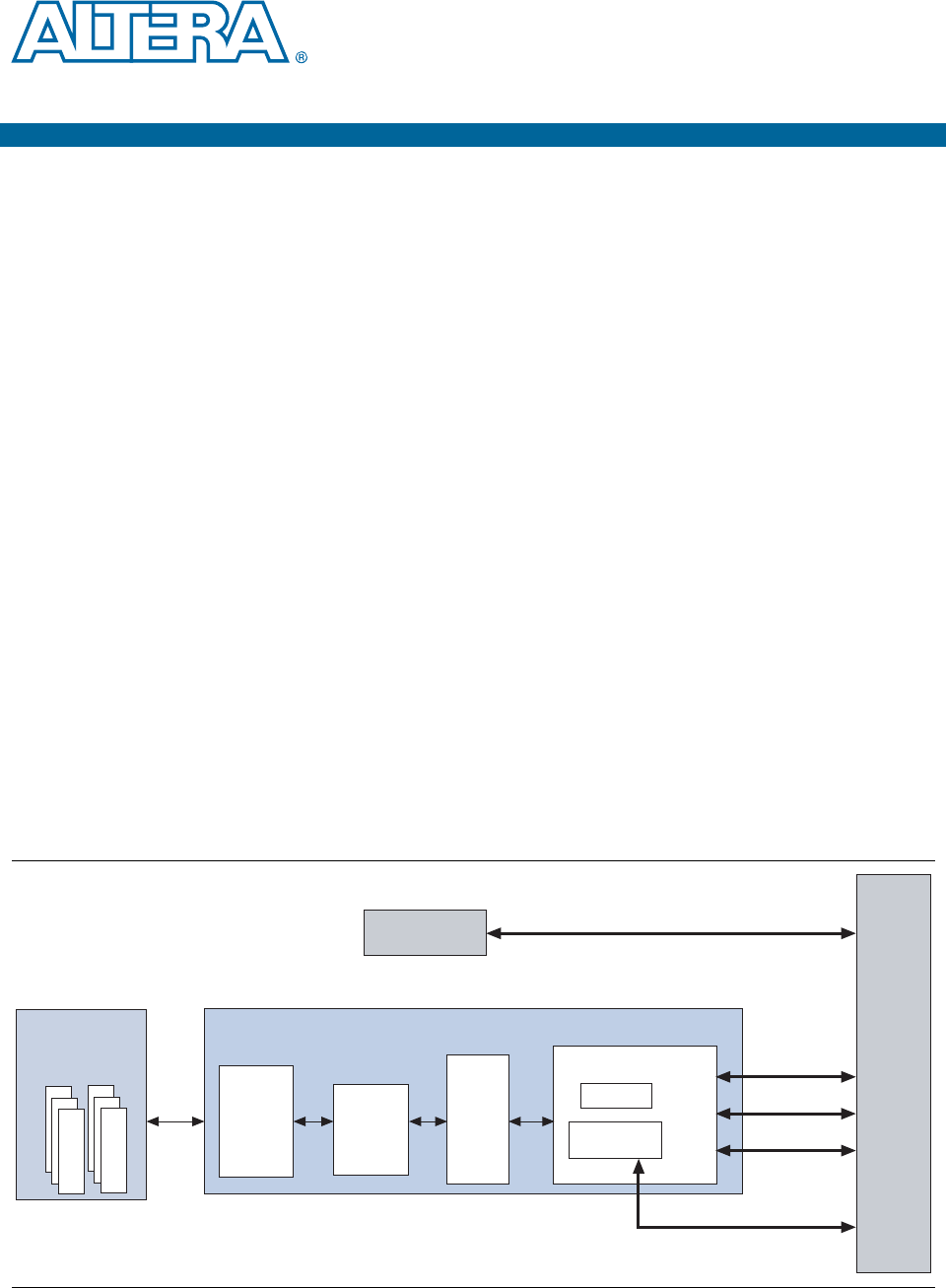

6. IP Core Architecture

This chapter describes the architecture of the Cyclone V Hard IP for PCI Express. The

Cyclone V Hard IP for PCI Express implements the complete PCI Express protocol

stack as defined in the PCI Express Base Specification 2.1. The protocol stack includes

the following layers:

■ Transaction Layer—The Transaction Layer contains the Configuration Space, the RX

and TX channels, the RX buffer, and flow control credits.

■ Data Link Layer—The Data Link Layer, located between the Physical Layer and the

Transaction Layer, manages packet transmission and maintains data integrity at

the link level. Specifically, the Data Link Layer performs the following tasks:

■ Manages transmission and reception of Data Link Layer Packets (DLLPs)

■ Generates all transmission cyclical redundancy code (CRC) values and checks

all CRCs during reception

■ Manages the retry buffer and retry mechanism according to received

ACK/NAK Data Link Layer packets

■ Initializes the flow control mechanism for DLLPs and routes flow control

credits to and from the Transaction Layer

■ Physical Layer—The Physical Layer initializes the speed, lane numbering, and lane

width of the PCI Express link according to packets received from the link and

directives received from higher layers.

Figure 6–1 provides a high-level block diagram of the CycloneV Hard IP for PCI

Express.

Figure 6–1. Cyclone V Hard IP for PCI Express with Avalon-ST Interface

Clock

Domain

Crossing

(CDC)

Data

Link

Layer

(DLL)

Transaction Layer (TL)

PHYMAC

Hard IP for PCI Express

Avalon-ST TX

Avalon-ST RX

Side Band

Local

Management

Interface (LMI)

PIPE

Application

Layer

Clock & Reset

Selection

Configuration

Space

PCSPMA

Physical Layer

(Transceivers)

RX Buffer

PHY IP Core for

PCI Express (PIPE)

December 2013

UG-01110-1.5