User guide

Table Of Contents

- Cyclone V Hard IP for PCI Express User Guide

- Contents

- 1. Datasheet

- 2. Getting Started with the Cyclone V Hard IP for PCI Express

- 3. Getting Started with the Avalon-MM Cyclone Hard IP for PCI Express

- Running Qsys

- Customizing the Cyclone VHard IP for PCI Express IP Core

- Adding the Remaining Components to the Qsys System

- Completing the Connections in Qsys

- Specifying Clocks and Interrupts

- Specifying Exported Interfaces

- Specifying Address Assignments

- Simulating the Example Design

- Simulating the Single DWord Design

- Understanding Channel Placement Guidelines

- Adding Synopsis Design Constraints

- Creating a Quartus II Project

- Compiling the Design

- Programming a Device

- 4. Parameter Settings for the Cyclone V Hard IP for PCI Express

- 5. Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

- 6. IP Core Architecture

- Key Interfaces

- Protocol Layers

- Multi-Function Support

- PCI Express Avalon-MM Bridge

- Avalon-MM Bridge TLPs

- Avalon-MM-to-PCI Express Write Requests

- Avalon-MM-to-PCI Express Upstream Read Requests

- PCI Express-to-Avalon-MM Read Completions

- PCI Express-to-Avalon-MM Downstream Write Requests

- PCI Express-to-Avalon-MM Downstream Read Requests

- Avalon-MM-to-PCI Express Read Completions

- PCI Express-to-Avalon-MM Address Translation for Endpoints

- Minimizing BAR Sizes and the PCIe Address Space

- Avalon-MM-to-PCI Express Address Translation Algorithm

- Single DWord Completer Endpoint

- 7. IP Core Interfaces

- Cyclone V Hard IP for PCI Express

- Avalon-MM Hard IP for PCI Express

- Physical Layer Interface Signals

- Test Signals

- 8. Register Descriptions

- Configuration Space Register Content

- Altera-Defined Vendor Specific Extended Capability (VSEC)

- PCI Express Avalon-MM Bridge Control Register Access Content

- Avalon-MM to PCI Express Interrupt Registers

- PCI Express Mailbox Registers

- Avalon-MM-to-PCI Express Address Translation Table

- Root Port TLP Data Registers

- Programming Model for Avalon-MM Root Port

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

- Avalon-MM Mailbox Registers

- Correspondence between Configuration Space Registers and the PCIe Spec 2.1

- 9. Reset and Clocks

- 10. Transaction Layer Protocol (TLP) Details

- 11. Interrupts

- Interrupts for Endpoints Using the Avalon-ST Application Interface

- Interrupts for Root Ports Using the Avalon-ST Interface to the Application Layer

- Interrupts for Endpoints Using the Avalon-MM Interface to the Application Layer

- Interrupts for End Points Using the Avalon-MM Interface with Multiple MSI/MSI-X Support

- 12. Optional Features

- 13. Flow Control

- 14. Error Handling

- 15. Transceiver PHY IP Reconfiguration

- 16. SDC Timing Constraints

- 17. Testbench and Design Example

- Endpoint Testbench

- Root Port Testbench

- Chaining DMA Design Examples

- Test Driver Module

- Root Port Design Example

- Root Port BFM

- BFM Procedures and Functions

- 18. Debugging

- A. Transaction Layer Packet (TLP) Header Formats

- Additional Information

5–4 Chapter 5: Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

PCI Express/PCI Capabilities

Cyclone V Hard IP for PCI Express December 2013 Altera Corporation

User Guide

Device

Table 5–4 describes the device parameters.

1 Some of these parameters are stored in the Common Configuration Space Header.

Text in green are links to these parameters stored in the Common Configuration Space

Header.

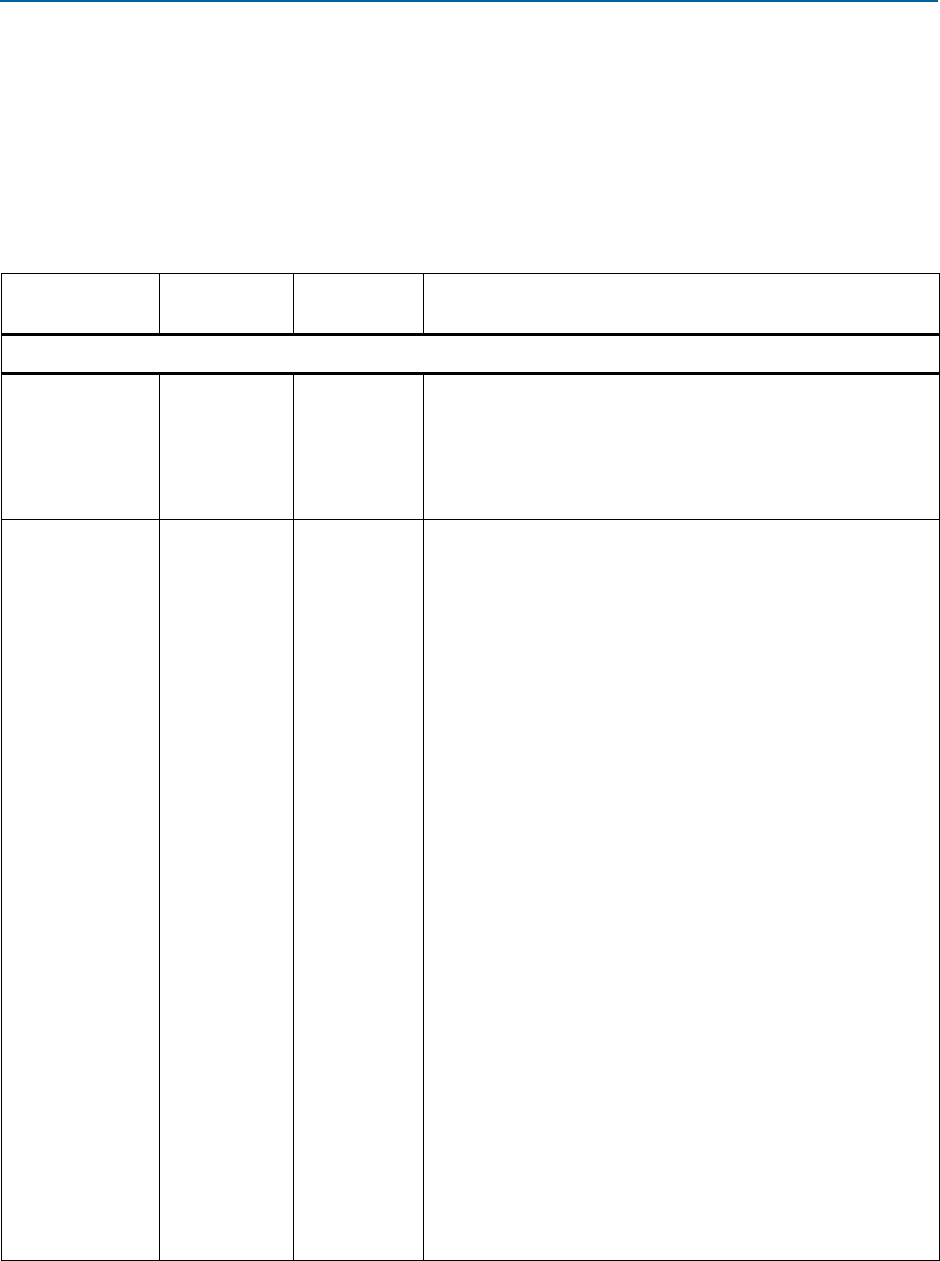

Table 5–4. Capabilities Registers for Function <n> (Part 1 of 2)

Parameter

Possible

Values

Default

Value

Description

Device Capabilities

Maximum

payload size

0x084

128 bytes

256 bytes

128 bytes

Specifies the maximum payload size supported. This

parameter sets the read-only value of the max payload size

supported field of the Device Capabilities register (0x084[2:0])

and optimizes the IP core for this size payload. You should

optimize this setting based on your typical expected

transaction sizes.

Completion

timeout range

ABCD

BCD

ABC

AB

B

A

None

ABCD

Indicates device function support for the optional completion

timeout programmability mechanism. This mechanism allows

system software to modify the completion timeout value. This

field is applicable only to Root Ports and Endpoints that issue

requests on their own behalf. Completion timeouts are

specified and enabled in the Device Control 2 register (0x0A8)

of the PCI Express Capability Structure Version 2.0 described

in Table 8–8 on page 8–4. For all other functions this field is

reserved and must be hardwired to 0x0000b. Four time value

ranges are defined:

■ Range A: 50 µs to 10 ms

■ Range B: 10 ms to 250 ms

■ Range C: 250 ms to 4 s

■ Range D: 4 s to 64 s

Bits are set to show timeout value ranges supported. 0x0000b

completion timeout programming is not supported and the

function must implement a timeout value in the range 50 s to

50 ms.

The following encodings are used to specify the range:

■ 0001 Range A

■ 0010 Range B

■ 0011 Ranges A and B

■ 0110 Ranges B and C

■ 0111 Ranges A, B, and C

■ 1110 Ranges B, C and D

■ 1111 Ranges A, B, C, and D