User guide

Table Of Contents

- Cyclone V Hard IP for PCI Express User Guide

- Contents

- 1. Datasheet

- 2. Getting Started with the Cyclone V Hard IP for PCI Express

- 3. Getting Started with the Avalon-MM Cyclone Hard IP for PCI Express

- Running Qsys

- Customizing the Cyclone VHard IP for PCI Express IP Core

- Adding the Remaining Components to the Qsys System

- Completing the Connections in Qsys

- Specifying Clocks and Interrupts

- Specifying Exported Interfaces

- Specifying Address Assignments

- Simulating the Example Design

- Simulating the Single DWord Design

- Understanding Channel Placement Guidelines

- Adding Synopsis Design Constraints

- Creating a Quartus II Project

- Compiling the Design

- Programming a Device

- 4. Parameter Settings for the Cyclone V Hard IP for PCI Express

- 5. Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

- 6. IP Core Architecture

- Key Interfaces

- Protocol Layers

- Multi-Function Support

- PCI Express Avalon-MM Bridge

- Avalon-MM Bridge TLPs

- Avalon-MM-to-PCI Express Write Requests

- Avalon-MM-to-PCI Express Upstream Read Requests

- PCI Express-to-Avalon-MM Read Completions

- PCI Express-to-Avalon-MM Downstream Write Requests

- PCI Express-to-Avalon-MM Downstream Read Requests

- Avalon-MM-to-PCI Express Read Completions

- PCI Express-to-Avalon-MM Address Translation for Endpoints

- Minimizing BAR Sizes and the PCIe Address Space

- Avalon-MM-to-PCI Express Address Translation Algorithm

- Single DWord Completer Endpoint

- 7. IP Core Interfaces

- Cyclone V Hard IP for PCI Express

- Avalon-MM Hard IP for PCI Express

- Physical Layer Interface Signals

- Test Signals

- 8. Register Descriptions

- Configuration Space Register Content

- Altera-Defined Vendor Specific Extended Capability (VSEC)

- PCI Express Avalon-MM Bridge Control Register Access Content

- Avalon-MM to PCI Express Interrupt Registers

- PCI Express Mailbox Registers

- Avalon-MM-to-PCI Express Address Translation Table

- Root Port TLP Data Registers

- Programming Model for Avalon-MM Root Port

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

- Avalon-MM Mailbox Registers

- Correspondence between Configuration Space Registers and the PCIe Spec 2.1

- 9. Reset and Clocks

- 10. Transaction Layer Protocol (TLP) Details

- 11. Interrupts

- Interrupts for Endpoints Using the Avalon-ST Application Interface

- Interrupts for Root Ports Using the Avalon-ST Interface to the Application Layer

- Interrupts for Endpoints Using the Avalon-MM Interface to the Application Layer

- Interrupts for End Points Using the Avalon-MM Interface with Multiple MSI/MSI-X Support

- 12. Optional Features

- 13. Flow Control

- 14. Error Handling

- 15. Transceiver PHY IP Reconfiguration

- 16. SDC Timing Constraints

- 17. Testbench and Design Example

- Endpoint Testbench

- Root Port Testbench

- Chaining DMA Design Examples

- Test Driver Module

- Root Port Design Example

- Root Port BFM

- BFM Procedures and Functions

- 18. Debugging

- A. Transaction Layer Packet (TLP) Header Formats

- Additional Information

Info–4 Typographic Conventions

Cyclone V Hard IP for PCI Express December 2013 Altera Corporation

User Guide

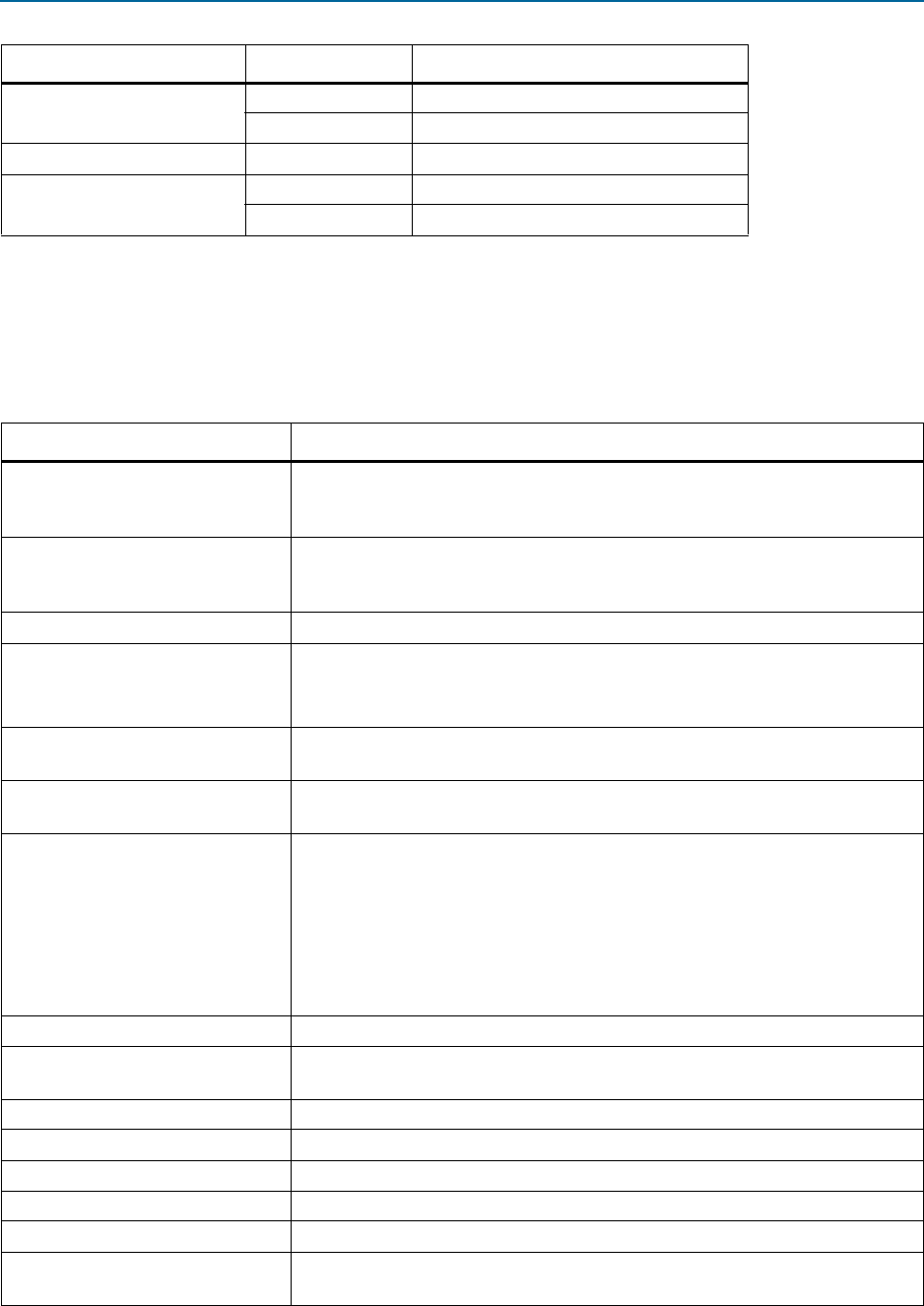

Typographic Conventions

The following table shows the typographic conventions this document uses.

Technical training

Website www.altera.com/training

Email custrain@altera.com

Product literature Website www.altera.com/literature

Nontechnical support (general) Email nacomp@altera.com

(software licensing) Email authorization@altera.com

Note to Table:

(1) You can also contact your local Altera sales office or sales representative.

Visual Cue Meaning

Bold Type with Initial Capital

Letters

Indicate command names, dialog box titles, dialog box options, and other GUI

labels. For example, Save As dialog box. For GUI elements, capitalization matches

the GUI.

bold type

Indicates directory names, project names, disk drive names, file names, file name

extensions, software utility names, and GUI labels. For example, \qdesigns

directory, D: drive, and chiptrip.gdf file.

Italic Type with Initial Capital Letters Indicate document titles. For example, Stratix IV Design Guidelines.

italic type

Indicates variables. For example, n + 1.

Variable names are enclosed in angle brackets (< >). For example, <file name> and

<project name>.pof file.

Initial Capital Letters

Indicate keyboard keys and menu names. For example, the Delete key and the

Options menu.

“Subheading Title”

Quotation marks indicate references to sections in a document and titles of

Quartus II Help topics. For example, “Typographic Conventions.”

Courier type

Indicates signal, port, register, bit, block, and primitive names. For example,

data1

,

tdi

, and

input

. The suffix

n

denotes an active-low signal. For example,

resetn

.

Indicates command line commands and anything that must be typed exactly as it

appears. For example,

c:\qdesigns\tutorial\chiptrip.gdf

.

Also indicates sections of an actual file, such as a Report File, references to parts of

files (for example, the AHDL keyword

SUBDESIGN

), and logic function names (for

example,

TRI

).

r An angled arrow instructs you to press the Enter key.

1., 2., 3., and

a., b., c., and so on

Numbered steps indicate a list of items when the sequence of the items is important,

such as the steps listed in a procedure.

■ ■ ■ Bullets indicate a list of items when the sequence of the items is not important.

1 The hand points to information that requires special attention.

h The question mark directs you to a software help system with related information.

f The feet direct you to another document or website with related information.

m The multimedia icon directs you to a related multimedia presentation.

c

A caution calls attention to a condition or possible situation that can damage or

destroy the product or your work.

Contact

(1)

Contact Method Address