User guide

Table Of Contents

- Cyclone V Hard IP for PCI Express User Guide

- Contents

- 1. Datasheet

- 2. Getting Started with the Cyclone V Hard IP for PCI Express

- 3. Getting Started with the Avalon-MM Cyclone Hard IP for PCI Express

- Running Qsys

- Customizing the Cyclone VHard IP for PCI Express IP Core

- Adding the Remaining Components to the Qsys System

- Completing the Connections in Qsys

- Specifying Clocks and Interrupts

- Specifying Exported Interfaces

- Specifying Address Assignments

- Simulating the Example Design

- Simulating the Single DWord Design

- Understanding Channel Placement Guidelines

- Adding Synopsis Design Constraints

- Creating a Quartus II Project

- Compiling the Design

- Programming a Device

- 4. Parameter Settings for the Cyclone V Hard IP for PCI Express

- 5. Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

- 6. IP Core Architecture

- Key Interfaces

- Protocol Layers

- Multi-Function Support

- PCI Express Avalon-MM Bridge

- Avalon-MM Bridge TLPs

- Avalon-MM-to-PCI Express Write Requests

- Avalon-MM-to-PCI Express Upstream Read Requests

- PCI Express-to-Avalon-MM Read Completions

- PCI Express-to-Avalon-MM Downstream Write Requests

- PCI Express-to-Avalon-MM Downstream Read Requests

- Avalon-MM-to-PCI Express Read Completions

- PCI Express-to-Avalon-MM Address Translation for Endpoints

- Minimizing BAR Sizes and the PCIe Address Space

- Avalon-MM-to-PCI Express Address Translation Algorithm

- Single DWord Completer Endpoint

- 7. IP Core Interfaces

- Cyclone V Hard IP for PCI Express

- Avalon-MM Hard IP for PCI Express

- Physical Layer Interface Signals

- Test Signals

- 8. Register Descriptions

- Configuration Space Register Content

- Altera-Defined Vendor Specific Extended Capability (VSEC)

- PCI Express Avalon-MM Bridge Control Register Access Content

- Avalon-MM to PCI Express Interrupt Registers

- PCI Express Mailbox Registers

- Avalon-MM-to-PCI Express Address Translation Table

- Root Port TLP Data Registers

- Programming Model for Avalon-MM Root Port

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

- Avalon-MM Mailbox Registers

- Correspondence between Configuration Space Registers and the PCIe Spec 2.1

- 9. Reset and Clocks

- 10. Transaction Layer Protocol (TLP) Details

- 11. Interrupts

- Interrupts for Endpoints Using the Avalon-ST Application Interface

- Interrupts for Root Ports Using the Avalon-ST Interface to the Application Layer

- Interrupts for Endpoints Using the Avalon-MM Interface to the Application Layer

- Interrupts for End Points Using the Avalon-MM Interface with Multiple MSI/MSI-X Support

- 12. Optional Features

- 13. Flow Control

- 14. Error Handling

- 15. Transceiver PHY IP Reconfiguration

- 16. SDC Timing Constraints

- 17. Testbench and Design Example

- Endpoint Testbench

- Root Port Testbench

- Chaining DMA Design Examples

- Test Driver Module

- Root Port Design Example

- Root Port BFM

- BFM Procedures and Functions

- 18. Debugging

- A. Transaction Layer Packet (TLP) Header Formats

- Additional Information

17–2 Chapter 17: Testbench and Design Example

Endpoint Testbench

Cyclone V Hard IP for PCI Express December 2013 Altera Corporation

User Guide

■ It can only handle received read requests that are less than or equal to the

currently set Maximum payload size option specified under PCI Express/PCI

Capabilites heading under the Device tab using the parameter editor. Many

systems are capable of handling larger read requests that are then returned in

multiple completions.

■ It always returns a single completion for every read request. Some systems split

completions on every 64-byte address boundary.

■ It always returns completions in the same order the read requests were issued.

Some systems generate the completions out-of-order.

■ It is unable to generate zero-length read requests that some systems generate as

flush requests following some write transactions. The Application Layer must be

capable of generating the completions to the zero length read requests.

■ It uses fixed credit allocation.

■ It does not support parity.

■ It does not support multi-function designs.

Endpoint Testbench

After you install the Quartus II software for 11.1, you can copy any of the five example

designs from the <install_dir>/ip/altera/altera_pcie/altera_pcie_hip_ast_ed

/example_design directory. You can generate the testbench from the example design

as was shown in Chapter 2, Getting Started with the Cyclone V Hard IP for PCI

Express.

This testbench simulates up to an ×8 PCI Express link using either the PIPE interfaces

of the Root Port and Endpoints or the serial PCI Express interface. The testbench

design does not allow more than one PCI Express link to be simulated at a time.

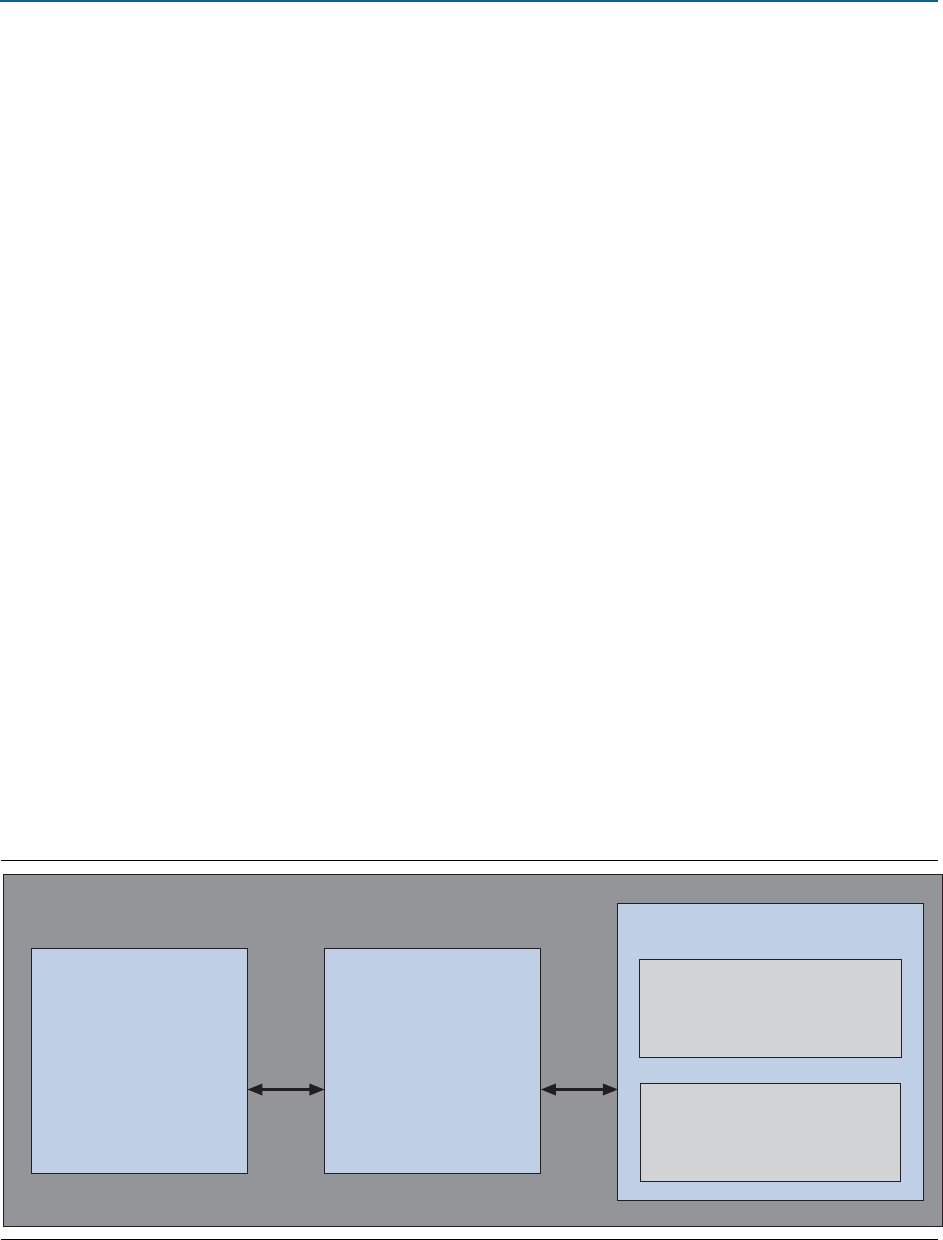

Figure 17–1 presents a high level view of the design example.

The top-level of the testbench instantiates four main modules:

Figure 17–1. Design Example for Endpoint Designs

APPS

altpcied_sv_hwtcl.v

Hard IP for PCI Express Testbench for Endpoints

Avalon-ST TX

Avalon-ST RX

reset

status

Avalon-ST TX

Avalon-ST RX

reset

status

DUT

altpcie_sv_hip_ast_hwtcl.v

Root Port Model

altpcie_tbed_sv_hwtcl.v

PIPE or

Serial

Interface

Root Port BFM

altpcietb_bfm_rpvar_64b_x4_pipen1b

Root Port Driver and Monitor

altpcietb_bfm_vc_intf