User guide

Table Of Contents

- Cyclone V Hard IP for PCI Express User Guide

- Contents

- 1. Datasheet

- 2. Getting Started with the Cyclone V Hard IP for PCI Express

- 3. Getting Started with the Avalon-MM Cyclone Hard IP for PCI Express

- Running Qsys

- Customizing the Cyclone VHard IP for PCI Express IP Core

- Adding the Remaining Components to the Qsys System

- Completing the Connections in Qsys

- Specifying Clocks and Interrupts

- Specifying Exported Interfaces

- Specifying Address Assignments

- Simulating the Example Design

- Simulating the Single DWord Design

- Understanding Channel Placement Guidelines

- Adding Synopsis Design Constraints

- Creating a Quartus II Project

- Compiling the Design

- Programming a Device

- 4. Parameter Settings for the Cyclone V Hard IP for PCI Express

- 5. Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

- 6. IP Core Architecture

- Key Interfaces

- Protocol Layers

- Multi-Function Support

- PCI Express Avalon-MM Bridge

- Avalon-MM Bridge TLPs

- Avalon-MM-to-PCI Express Write Requests

- Avalon-MM-to-PCI Express Upstream Read Requests

- PCI Express-to-Avalon-MM Read Completions

- PCI Express-to-Avalon-MM Downstream Write Requests

- PCI Express-to-Avalon-MM Downstream Read Requests

- Avalon-MM-to-PCI Express Read Completions

- PCI Express-to-Avalon-MM Address Translation for Endpoints

- Minimizing BAR Sizes and the PCIe Address Space

- Avalon-MM-to-PCI Express Address Translation Algorithm

- Single DWord Completer Endpoint

- 7. IP Core Interfaces

- Cyclone V Hard IP for PCI Express

- Avalon-MM Hard IP for PCI Express

- Physical Layer Interface Signals

- Test Signals

- 8. Register Descriptions

- Configuration Space Register Content

- Altera-Defined Vendor Specific Extended Capability (VSEC)

- PCI Express Avalon-MM Bridge Control Register Access Content

- Avalon-MM to PCI Express Interrupt Registers

- PCI Express Mailbox Registers

- Avalon-MM-to-PCI Express Address Translation Table

- Root Port TLP Data Registers

- Programming Model for Avalon-MM Root Port

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

- Avalon-MM Mailbox Registers

- Correspondence between Configuration Space Registers and the PCIe Spec 2.1

- 9. Reset and Clocks

- 10. Transaction Layer Protocol (TLP) Details

- 11. Interrupts

- Interrupts for Endpoints Using the Avalon-ST Application Interface

- Interrupts for Root Ports Using the Avalon-ST Interface to the Application Layer

- Interrupts for Endpoints Using the Avalon-MM Interface to the Application Layer

- Interrupts for End Points Using the Avalon-MM Interface with Multiple MSI/MSI-X Support

- 12. Optional Features

- 13. Flow Control

- 14. Error Handling

- 15. Transceiver PHY IP Reconfiguration

- 16. SDC Timing Constraints

- 17. Testbench and Design Example

- Endpoint Testbench

- Root Port Testbench

- Chaining DMA Design Examples

- Test Driver Module

- Root Port Design Example

- Root Port BFM

- BFM Procedures and Functions

- 18. Debugging

- A. Transaction Layer Packet (TLP) Header Formats

- Additional Information

7–4 Chapter 7: IP Core Interfaces

Cyclone V Hard IP for PCI Express

Cyclone V Hard IP for PCI Express December 2013 Altera Corporation

User Guide

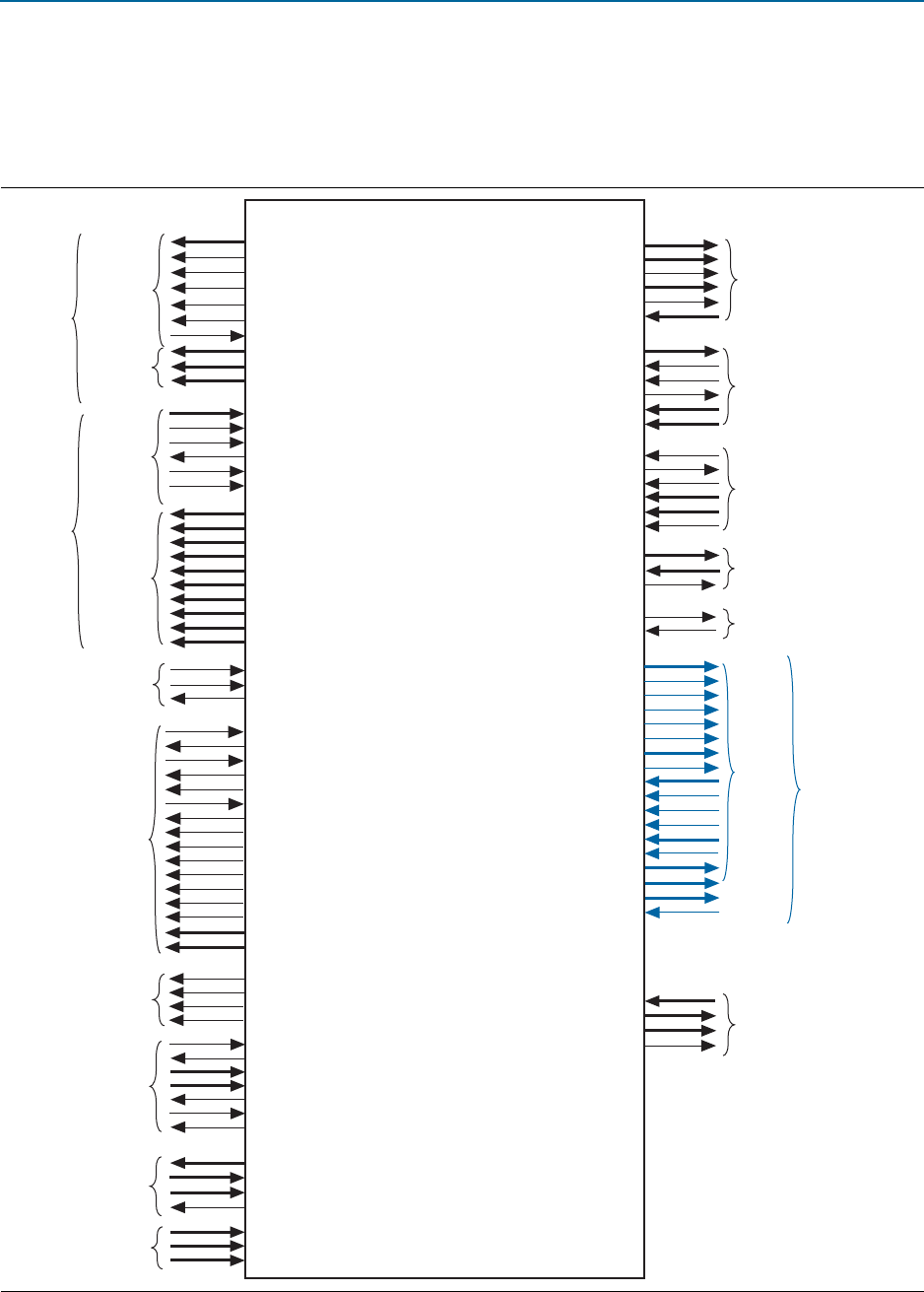

Figure 7–3 illustrates the top-level signals in Cyclone V Hard IP for PCI Express IP

core. Signal names that include <a> also exist for functions 1 to 7.

Figure 7–3. Signals in the Cyclone V Hard IP for PCI Express with Avalon-ST Interface

rx_st_data[63:0]

rx_st_sop

rx_st_eop

rx_st_ready

rx_st_valid

rx_st_err

rx_st_mask

rx_st_bar[7:0]

rx_st_be[7:0]

rx_bar_dec_func_num[2:0]

Cyclone V Hard IP for PCI Express, Avalon-ST Interface

Test

Interface

RX Port

tx_st_data[63:0]

tx_st_sop

tx_st_eop

tx_st_ready

tx_st_valid

tx_st_err

tx_cred_datafccp[11:0]

tx_cred_datafcnp[11:0]

tx_cred_datafcp[11:0]

tx_cred_fchipons[5:0]

tx_cred_fcinfinite[5:0]

tx_cred_hdrfccp[7:0]

tx_cred_hdrfcnp[7:0]

tx_cred_hdrfcp[7:0]

ko_cpl_spc_header[7:0]

ko_cpl_spc_data[11:0]

Clocks

Power

Managementt

Transaction Layer

Configuration

ECC Error

Completion

Interface

LMI

txdata0[7:0]

txdatak0

txdetectrx0

txelecidle0

txcompl0

rxpolarity0

powerdown0[1:0]

tx_deemph

rxdata0[7:0]

rxdatak0

rxvalid0

phystatus0

eidleinferset0[[2:0]

rxelecidle0

rxstatus0[2:0]

sim_ltssmstate[4:0]

sim_pipe_rate[1:0]

sim_pipe_pclk_in

8-bit

PIPE

test_in[31:0]

simu_pipe_mode

lane_act[3:0]

testin_zero

tl_cfg_add[6:0]

tl_cfg_ctl[31:0]

tl_cfg_ctl_wr

tl_cfg_sts[122:0]

tl_cfg_sts_wr

tl_hpg_ctrl_er[4:0]

lmi_dout[31:0]

lmi_rden

lmi_wren

lmi_ack

lmi_addr[14:0]

lmi_din[31:0]

reconfig_fromxcvr[<n>69-1:0]

reconfig_toxcvr[<n>45-1:0]

busy_xcvr_reconfig

Transceiver

Reconfiguration

for internal PHY

x number of lanes

tx_out0

rx_in0

Serial IF to PIPE

Avalon-ST

Avalon-ST

Component

Specific

Component

Specific

TX

Credit

derr_cor_ext_rcv0

derr_cor_ext_rcv1

derr_rpl

derr_cor_ext_rpl0

Interrupts

(Root Port)

int_status[3:0]

aer_msi_num[4:0]

pex_msi_num[4:0]

serr_out

cpl_err[6:0]

cpl_pending[7:0]

cpl_err_func[2:0]

Interrupt

(Endpoint)

tl_app_msi_req

tl_app_msi_ack

tl_app_msi_tc[2:0]

tl_app_msi_num[4:0]

tl_app_msi_func[2:0]

tl_app_int<a>_sts

tl_app_int<a>_ack

tl_app_int<a>_funcnum[2:0]

pme_to_cr

pme_to_sr

pm_event

pm_event_func[2:0]

pm_data[9:0]

pm_auxpwr

refclk

pld_clk

coreclkout

npor

reset_status

pin_perst

sedes_pll_locked

fixedclk_locked

pld_core_ready

pld_clk_inuse

dlup

dlup_exit

ratetiedtognd

ev128ns

ev1us

hotrst_exit

l2_exit

current_speed[1:0]

dl_ltssm[4:0]

Reset &

Lock Status

PIPE

Interface

for Simulation

and Hardware

Debug Using

dl_ltssm[4:0]

in SignalTap