User guide

Table Of Contents

- Cyclone V Hard IP for PCI Express User Guide

- Contents

- 1. Datasheet

- 2. Getting Started with the Cyclone V Hard IP for PCI Express

- 3. Getting Started with the Avalon-MM Cyclone Hard IP for PCI Express

- Running Qsys

- Customizing the Cyclone VHard IP for PCI Express IP Core

- Adding the Remaining Components to the Qsys System

- Completing the Connections in Qsys

- Specifying Clocks and Interrupts

- Specifying Exported Interfaces

- Specifying Address Assignments

- Simulating the Example Design

- Simulating the Single DWord Design

- Understanding Channel Placement Guidelines

- Adding Synopsis Design Constraints

- Creating a Quartus II Project

- Compiling the Design

- Programming a Device

- 4. Parameter Settings for the Cyclone V Hard IP for PCI Express

- 5. Parameter Settings for the Avalon-MM Cyclone V Hard IP for PCI Express

- 6. IP Core Architecture

- Key Interfaces

- Protocol Layers

- Multi-Function Support

- PCI Express Avalon-MM Bridge

- Avalon-MM Bridge TLPs

- Avalon-MM-to-PCI Express Write Requests

- Avalon-MM-to-PCI Express Upstream Read Requests

- PCI Express-to-Avalon-MM Read Completions

- PCI Express-to-Avalon-MM Downstream Write Requests

- PCI Express-to-Avalon-MM Downstream Read Requests

- Avalon-MM-to-PCI Express Read Completions

- PCI Express-to-Avalon-MM Address Translation for Endpoints

- Minimizing BAR Sizes and the PCIe Address Space

- Avalon-MM-to-PCI Express Address Translation Algorithm

- Single DWord Completer Endpoint

- 7. IP Core Interfaces

- Cyclone V Hard IP for PCI Express

- Avalon-MM Hard IP for PCI Express

- Physical Layer Interface Signals

- Test Signals

- 8. Register Descriptions

- Configuration Space Register Content

- Altera-Defined Vendor Specific Extended Capability (VSEC)

- PCI Express Avalon-MM Bridge Control Register Access Content

- Avalon-MM to PCI Express Interrupt Registers

- PCI Express Mailbox Registers

- Avalon-MM-to-PCI Express Address Translation Table

- Root Port TLP Data Registers

- Programming Model for Avalon-MM Root Port

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Root Ports

- PCI Express to Avalon-MM Interrupt Status and Enable Registers for Endpoints

- Avalon-MM Mailbox Registers

- Correspondence between Configuration Space Registers and the PCIe Spec 2.1

- 9. Reset and Clocks

- 10. Transaction Layer Protocol (TLP) Details

- 11. Interrupts

- Interrupts for Endpoints Using the Avalon-ST Application Interface

- Interrupts for Root Ports Using the Avalon-ST Interface to the Application Layer

- Interrupts for Endpoints Using the Avalon-MM Interface to the Application Layer

- Interrupts for End Points Using the Avalon-MM Interface with Multiple MSI/MSI-X Support

- 12. Optional Features

- 13. Flow Control

- 14. Error Handling

- 15. Transceiver PHY IP Reconfiguration

- 16. SDC Timing Constraints

- 17. Testbench and Design Example

- Endpoint Testbench

- Root Port Testbench

- Chaining DMA Design Examples

- Test Driver Module

- Root Port Design Example

- Root Port BFM

- BFM Procedures and Functions

- 18. Debugging

- A. Transaction Layer Packet (TLP) Header Formats

- Additional Information

1–2 Chapter 1: Datasheet

Features

Cyclone V Hard IP for PCI Express December 2013 Altera Corporation

User Guide

■ Qsys support using the Avalon Memory-Mapped (Avalon-MM) with a 64- or

128-bit interface to the Application Layer

■ Extended credit allocation settings to better optimize the RX buffer space based on

application type.

■ Qsys example designs demonstrating parameterization, design modules and

connectivity.

■ Optional end-to-end cyclic redundancy code (ECRC) generation and checking and

advanced error reporting (AER) for high reliability applications.

■ Easy to use:

■ Easy parameterization.

■ Substantial on-chip resource savings and guaranteed timing closure.

■ Easy adoption with no license requirement.

■ New features in the 13.1 release

■ Added support for Gen2 Configuration via Protocol (CvP) using an .ini file.

Contact your sales representative for more information.

.The Cyclone V Hard IP for PCI Express offers different features for the variants that

use the Avalon-ST interface to the Application Layer and the variants that use an

Avalon-MM interface to the Application Layer. Variants using the Avalon-ST interface

are available in both the MegaWizard Plug-In Manager and the Qsys design flows.

Variants using the Avalon-MM interface are only available in the Qsys design flow.

Variants using the Avalon-ST interfaces offer a richer feature set; however, if you are

not familiar with the PCI Express protocol, variants using the Avalon-MM interface

may be easier to understand. A PCI Express to Avalon-MM bridge translates the PCI

Express read, write and completion TLPs into standard Avalon-MM read and write

commands typically used by master and slave interfaces. Table 1–2 outlines these

differences in features between variants with Avalon-ST and Avalon-MM interfaces to

the Application Layer.

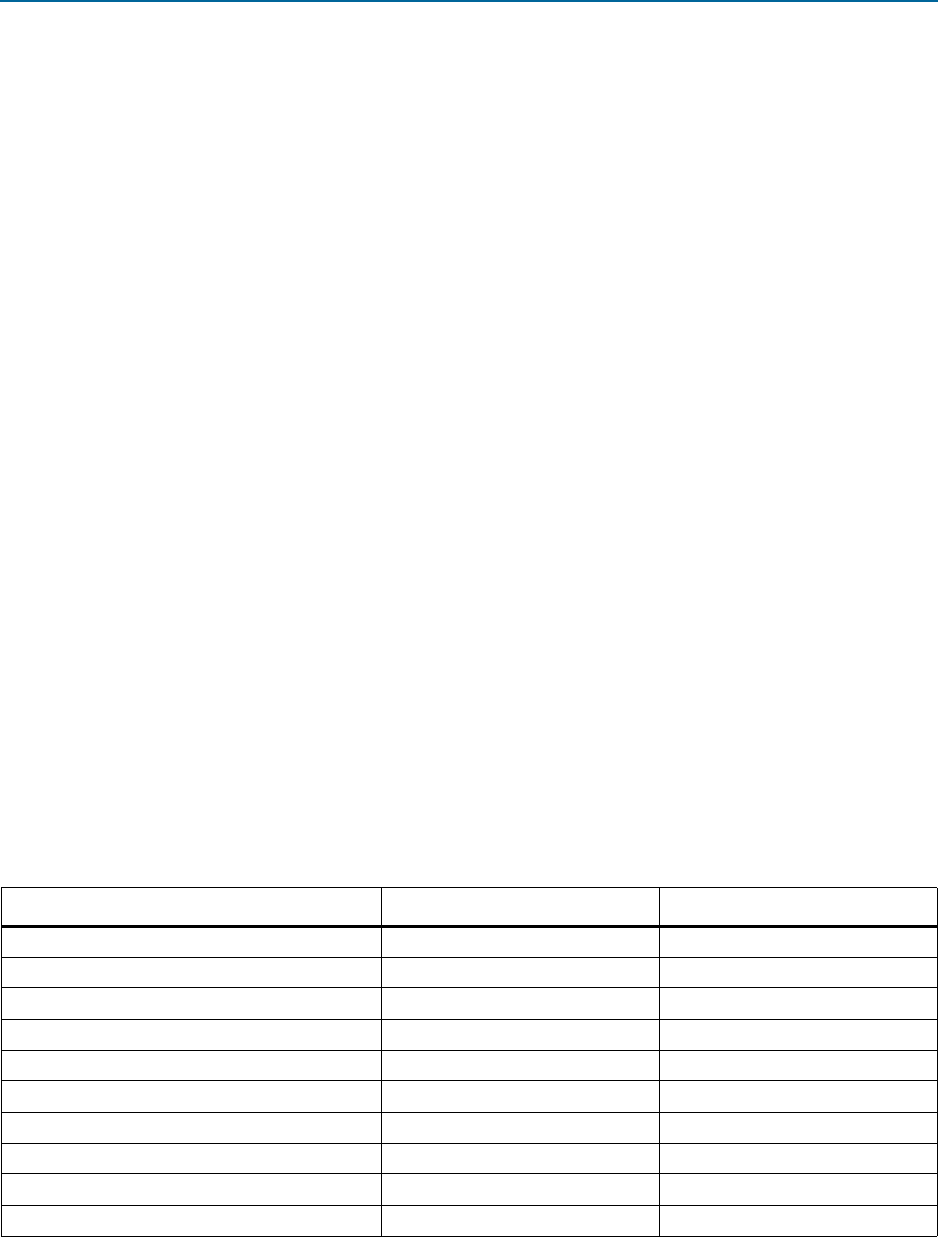

Table 1–1. Differences in Features Available Using the Avalon-MM and Avalon-ST Interfaces (Part 1 of 2)

Feature Avalon-ST Interface Avalon-MM Interface

MegaCore License Free Free

Native Endpoint Supported Supported

Legacy Endpoint (1) Supported Not Supported

Root port Supported Supported

Gen1 ×1, ×2, ×4 ×1, ×4 (2)

Gen2 ×1, ×2, ×4 ×1, ×4 (2)

MegaWizard Plug-In Manager design flow Supported Not supported

Qsys design flow Supported Supported

64-bit Application Layer interface Supported Supported

128-bit Application Layer interface Supported Supported