Datasheet

Table Of Contents

- DDR3L SDRAM

- Description

- State Diagram

- Functional Description

- Functional Block Diagrams

- Ball Assignments and Descriptions

- Package Dimensions

- Electrical Specifications

- Thermal Characteristics

- Electrical Specifications – I DD Specifications and Conditions

- Electrical Characteristics – 1.35V IDD Specifications

- Electrical Specifications – DC and AC

- ODT Characteristics

- Output Driver Impedance

- Output Characteristics and Operating Conditions

- Speed Bin Tables

- Electrical Characteristics and AC Operating Conditions

- Electrical Characteristics and AC Operating Conditions

- Command and Address Setup, Hold, and Derating

- Data Setup, Hold, and Derating

- Commands – Truth Tables

- Commands

- Input Clock Frequency Change

- Write Leveling

- Initialization

- Voltage Initialization / Change

- Mode Registers

- Mode Register 0 (MR0)

- Mode Register 1 (MR1)

- Mode Register 2 (MR2)

- Mode Register 3 (MR3)

- MODE REGISTER SET (MRS) Command

- ZQ CALIBRATION Operation

- ACTIVATE Operation

- READ Operation

- WRITE Operation

- PRECHARGE Operation

- SELF REFRESH Operation

- Extended Temperature Usage

- Power-Down Mode

- RESET Operation

- On-Die Termination (ODT)

- Dynamic ODT

- Synchronous ODT Mode

- Asynchronous ODT Mode

- Asynchronous to Synchronous ODT Mode Transition (Power-Down Exit)

Command and Address Setup, Hold, and Derating

The total

t

IS (setup time) and

t

IH (hold time) required is calculated by adding the data

sheet

t

IS (base) and

t

IH (base) values (see Table 57; values come from the Electrical

Characteristics and AC Operating Conditions table) to the Δ

t

IS and Δ

t

IH derating values

(see Table 58 (page 94), Table 59 (page 94) or Table 60 (page 94)) respectively. Ex-

ample:

t

IS (total setup time) =

t

IS (base) + Δ

t

IS. For a valid transition, the input signal

has to remain above/below V

IH(AC)

/V

IL(AC)

for some time

t

VAC (see Table 61 (page 95)).

Although the total setup time for slow slew rates might be negative (for example, a valid

input signal will not have reached V

IH(AC)

/V

IL(AC)

at the time of the rising clock transi-

tion), a valid input signal is still required to complete the transition and to reach

V

IH(AC)

/V

IL(AC)

(see Figure 11 (page 43) for input signal requirements). For slew rates that

fall between the values listed in Table 58 (page 94) and Table 60 (page 94), the derat-

ing values may be obtained by linear interpolation.

Setup (

t

IS) nominal slew rate for a rising signal is defined as the slew rate between the

last crossing of V

REF(DC)

and the first crossing of V

IH(AC)min

. Setup (

t

IS) nominal slew rate

for a falling signal is defined as the slew rate between the last crossing of V

REF(DC)

and

the first crossing of V

IL(AC)max

. If the actual signal is always earlier than the nominal slew

rate line between the shaded V

REF(DC)

-to-AC region, use the nominal slew rate for derat-

ing value (see Figure 30 (page 96)). If the actual signal is later than the nominal slew

rate line anywhere between the shaded V

REF(DC)

-to-AC region, the slew rate of a tangent

line to the actual signal from the AC level to the DC level is used for derating value (see

Figure 32 (page 98)).

Hold (

t

IH) nominal slew rate for a rising signal is defined as the slew rate between the

last crossing of V

IL(DC)max

and the first crossing of V

REF(DC)

. Hold (

t

IH) nominal slew rate

for a falling signal is defined as the slew rate between the last crossing of V

IH(DC)min

and

the first crossing of V

REF(DC)

. If the actual signal is always later than the nominal slew

rate line between the shaded DC-to-V

REF(DC)

region, use the nominal slew rate for derat-

ing value (see Figure 31 (page 97)). If the actual signal is earlier than the nominal slew

rate line anywhere between the shaded DC-to-V

REF(DC)

region, the slew rate of a tangent

line to the actual signal from the DC level to the V

REF(DC)

level is used for derating value

(see Figure 33 (page 99)).

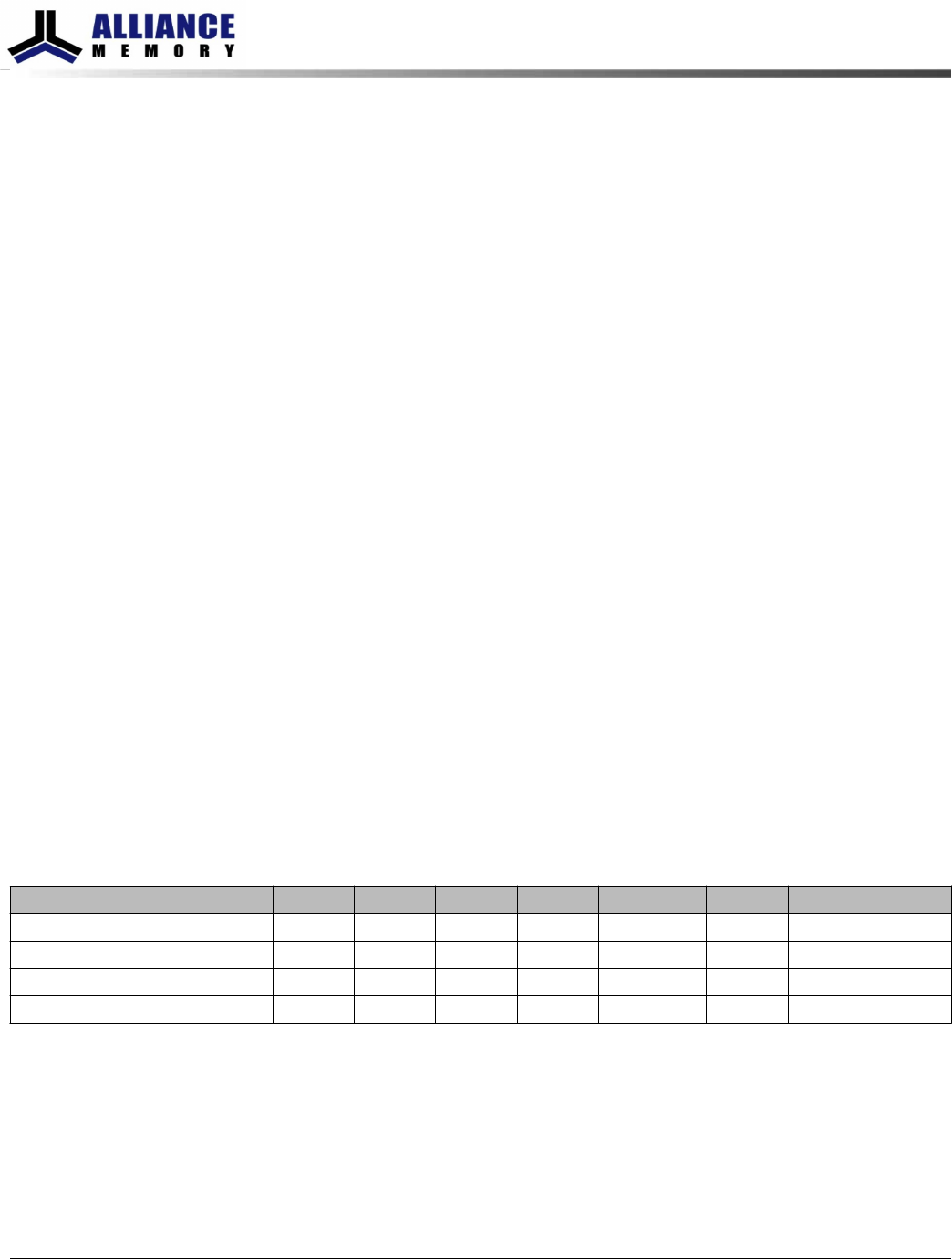

Table 57: DDR3L Command and Address Setup and Hold Values 1 V/ns Referenced – AC/DC-Based

Symbol 800 1066 1333 1600 1866 2133 Unit Reference

t

IS(base, AC160) 215 140 80 60 – – ps V

IH(AC)

/V

IL(AC)

t

IS(base, AC135) 365 290 205 185 65 60 ps V

IH(AC)

/V

IL(AC)

t

IS(base, AC125) ––––150135psV

IH(AC)

/V

IL(AC)

t

IH(base, DC90) 285 210 150 130 110 105 ps V

IH(DC)

/V

IL(DC)

8Gb: x4, x8, x16 DDR3L SDRAM

Command and Address Setup, Hold, and Derating

93

Rev 2.0 June 2016

© 2015 Alliance Memory, Inc. All rights reserved.

Alliance Memory Inc. reserves the right to change products or specification without notice

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070

TEL: (650) 610-6800 FAX: (650) 620-9211