Datasheet

Table Of Contents

- DDR3L SDRAM

- Description

- State Diagram

- Functional Description

- Functional Block Diagrams

- Ball Assignments and Descriptions

- Package Dimensions

- Electrical Specifications

- Thermal Characteristics

- Electrical Specifications – I DD Specifications and Conditions

- Electrical Characteristics – 1.35V IDD Specifications

- Electrical Specifications – DC and AC

- ODT Characteristics

- Output Driver Impedance

- Output Characteristics and Operating Conditions

- Speed Bin Tables

- Electrical Characteristics and AC Operating Conditions

- Electrical Characteristics and AC Operating Conditions

- Command and Address Setup, Hold, and Derating

- Data Setup, Hold, and Derating

- Commands – Truth Tables

- Commands

- Input Clock Frequency Change

- Write Leveling

- Initialization

- Voltage Initialization / Change

- Mode Registers

- Mode Register 0 (MR0)

- Mode Register 1 (MR1)

- Mode Register 2 (MR2)

- Mode Register 3 (MR3)

- MODE REGISTER SET (MRS) Command

- ZQ CALIBRATION Operation

- ACTIVATE Operation

- READ Operation

- WRITE Operation

- PRECHARGE Operation

- SELF REFRESH Operation

- Extended Temperature Usage

- Power-Down Mode

- RESET Operation

- On-Die Termination (ODT)

- Dynamic ODT

- Synchronous ODT Mode

- Asynchronous ODT Mode

- Asynchronous to Synchronous ODT Mode Transition (Power-Down Exit)

Output Characteristics and Operating Conditions

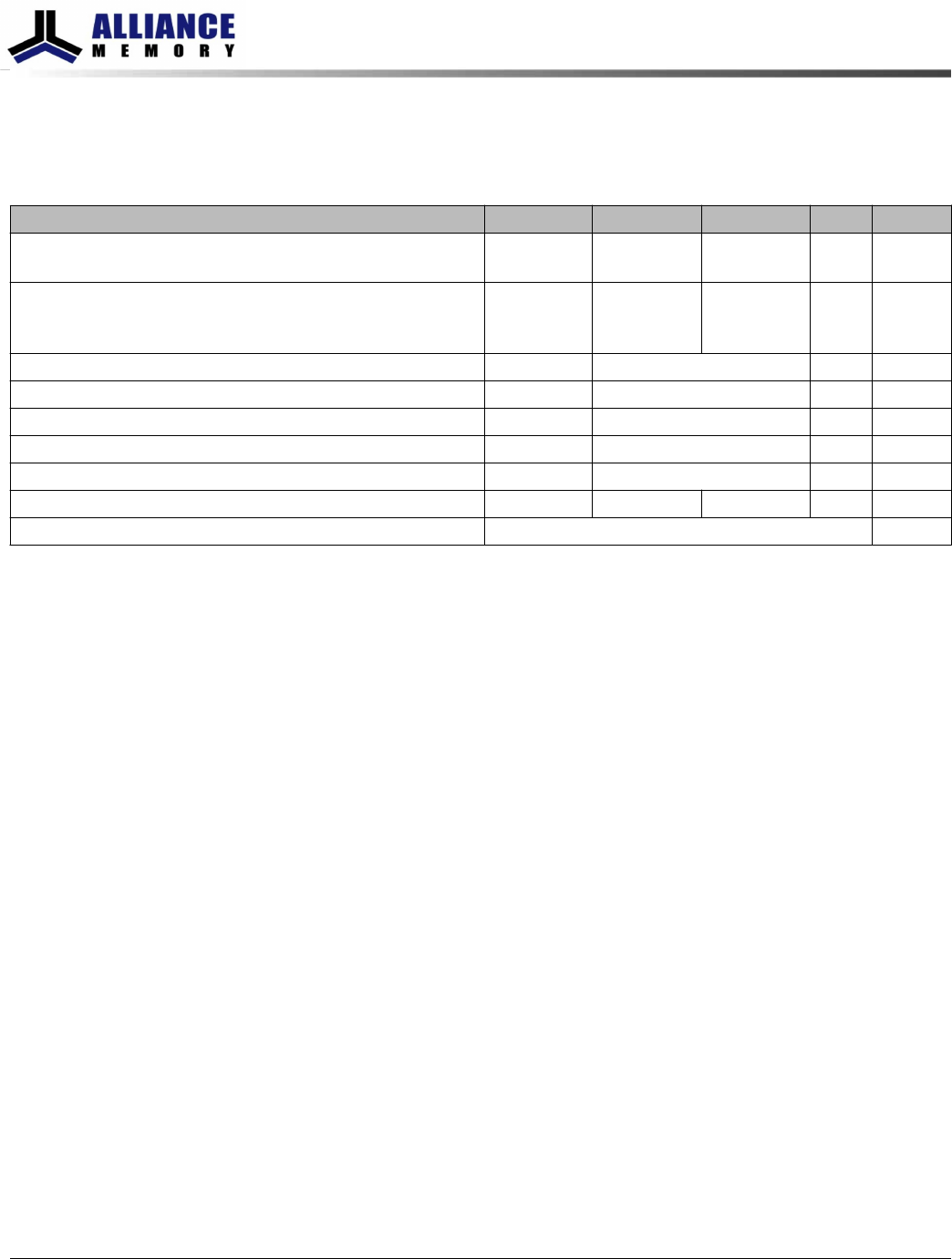

Table 45: DDR3L Single-Ended Output Driver Characteristics

All voltages are referenced to V

SS

Parameter/Condition Symbol Min Max Unit Notes

Output leakage current: DQ are disabled;

0V ≤ V

OUT

≤ V

DDQ

; ODT is disabled; ODT is HIGH

I

OZ

–5 5 μA 1

Output slew rate: Single-ended; For rising and falling edges,

measure between V

OL(AC)

= V

REF

- 0.09 × V

DDQ

and V

OH(AC)

=

V

REF

+ 0.09 × V

DDQ

SRQ

se

1.75 6 V/ns 1, 2, 3, 4

Single-ended DC high-level output voltage V

OH(DC)

0.8 × V

DDQ

V 1, 2, 5

Single-ended DC mid-point level output voltage V

OM(DC)

0.5 × V

DDQ

V 1, 2, 5

Single-ended DC low-level output voltage V

OL(DC)

0.2 × V

DDQ

V 1, 2, 5

Single-ended AC high-level output voltage V

OH(AC)

V

TT

+ 0.1 × V

DDQ

V 1, 2, 3, 6

Single-ended AC low-level output voltage V

OL(AC)

V

TT

- 0.1 × V

DDQ

V 1, 2, 3, 6

Delta R

ON

between pull-up and pull-down for DQ/DQS MM

PUPD

–10 10 % 1, 7

Test load for AC timing and output slew rates Output to V

TT

(V

DDQ

/2) via 25Ω resistor 3

Notes:

1. RZQ of 240Ω ±1% with RZQ/7 enabled (default 34Ω driver) and is applicable after prop-

er ZQ calibration has been performed at a stable temperature and voltage (V

DDQ

= V

DD

;

V

SSQ

= V

SS

).

2. V

TT

= V

DDQ

/2.

3. See Figure 27 (page 65) for the test load configuration.

4. The 6 V/ns maximum is applicable for a single DQ signal when it is switching either from

HIGH to LOW or LOW to HIGH while the remaining DQ signals in the same byte lane are

either all static or all switching in the opposite direction. For all other DQ signal switch-

ing combinations, the maximum limit of 6 V/ns is reduced to 5 V/ns.

5. See Figure 24 (page 56) for IV curve linearity. Do not use AC test load.

6. See Slew Rate Definitions for Single-Ended Output Signals (page 65) for output slew

rate.

7. See Figure 24 (page 56) for additional information.

8. See Figure 25 (page 63) for an example of a single-ended output signal.

8Gb: x4, x8, x16 DDR3L SDRAM

Output Characteristics and Operating Conditions

62

Rev 2.0 June 2016

© 2015 Alliance Memory, Inc. All rights reserved.

Alliance Memory Inc. reserves the right to change products or specification without notice

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070

TEL: (650) 610-6800 FAX: (650) 620-9211