Datasheet

Table Of Contents

- DDR3L SDRAM

- Description

- State Diagram

- Functional Description

- Functional Block Diagrams

- Ball Assignments and Descriptions

- Package Dimensions

- Electrical Specifications

- Thermal Characteristics

- Electrical Specifications – I DD Specifications and Conditions

- Electrical Characteristics – 1.35V IDD Specifications

- Electrical Specifications – DC and AC

- ODT Characteristics

- Output Driver Impedance

- Output Characteristics and Operating Conditions

- Speed Bin Tables

- Electrical Characteristics and AC Operating Conditions

- Electrical Characteristics and AC Operating Conditions

- Command and Address Setup, Hold, and Derating

- Data Setup, Hold, and Derating

- Commands – Truth Tables

- Commands

- Input Clock Frequency Change

- Write Leveling

- Initialization

- Voltage Initialization / Change

- Mode Registers

- Mode Register 0 (MR0)

- Mode Register 1 (MR1)

- Mode Register 2 (MR2)

- Mode Register 3 (MR3)

- MODE REGISTER SET (MRS) Command

- ZQ CALIBRATION Operation

- ACTIVATE Operation

- READ Operation

- WRITE Operation

- PRECHARGE Operation

- SELF REFRESH Operation

- Extended Temperature Usage

- Power-Down Mode

- RESET Operation

- On-Die Termination (ODT)

- Dynamic ODT

- Synchronous ODT Mode

- Asynchronous ODT Mode

- Asynchronous to Synchronous ODT Mode Transition (Power-Down Exit)

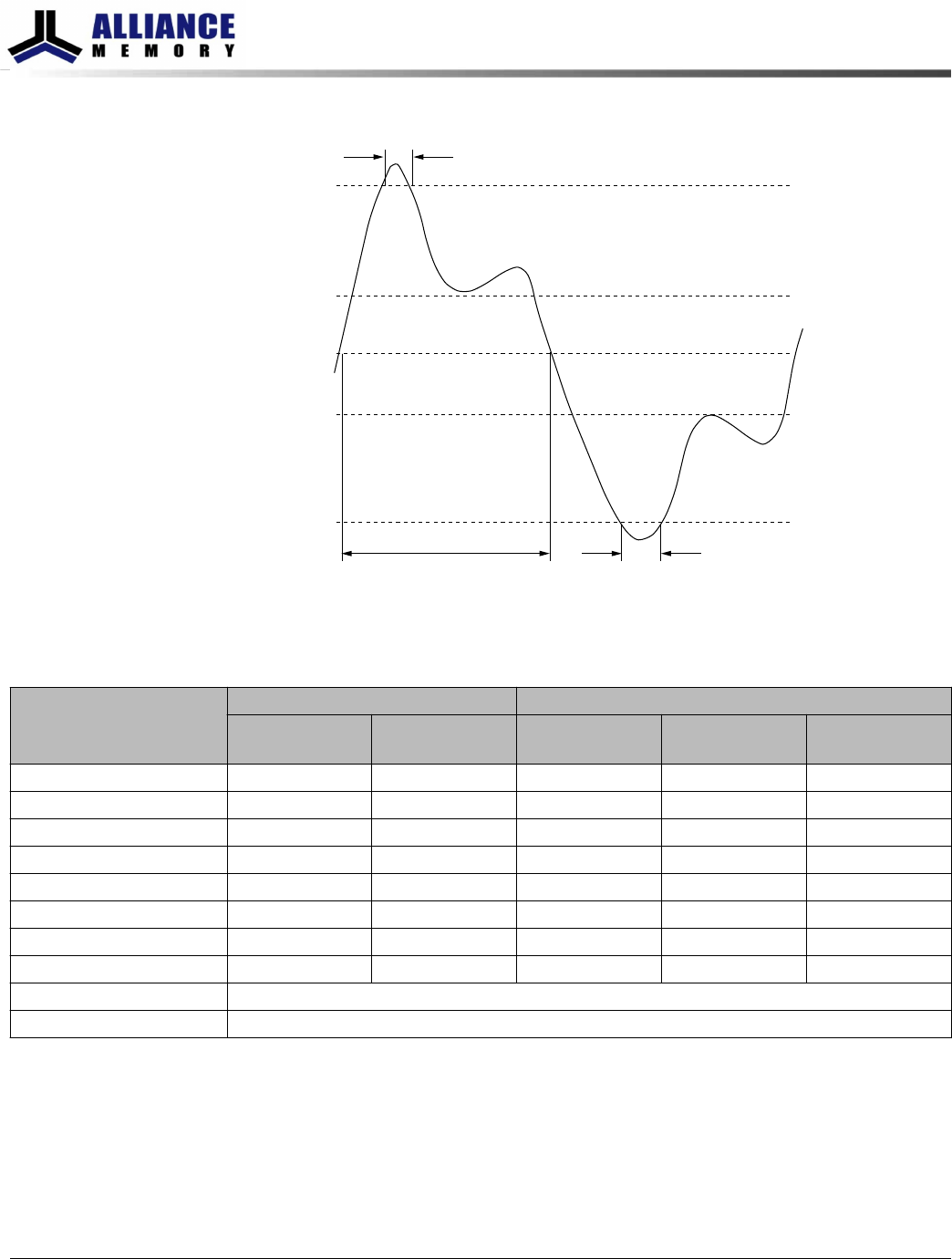

Figure 16: Definition of Differential AC-Swing and

t

DVAC

V

IH,diff(AC)min

0.0

V

IL,diff,max

t

DVAC

V

IH,diff,min

V

IL,diff(AC)max

Half cycle

t

DVAC

CK - CK#

DQS - DQS#

Table 26: DDR3L 1.35V – Minimum Required Time

t

DVAC for CK/CK#, DQS/DQS# Differential for AC

Ringback

Slew Rate (V/ns)

DDR3L-800/1066/1333/1600 DDR3L-1866/2133

t

DVAC at

320mV (ps)

t

DVAC at

270mV (ps)

t

DVAC at

270mV (ps)

t

DVAC at

250mV (ps)

t

DVAC at

260mV (ps)

>4.0 189 201 163 168 176

4.0 189 201 163 168 176

3.0 162 179 140 147 154

2.0 109 134 95 105 111

1.8 91 119 80 91 97

1.6 69 100 62 74 78

1.4 40 76 37 52 55

1.2 Note 1 44 5 22 24

1.0 Note 1

<1.0 Note 1

Note:

1. Rising input signal shall become equal to or greater than V

IH(AC)

level and Falling input

signal shall become equal to or less than V

IL(AC)

level.

8Gb: x4, x8, x16 DDR3L SDRAM

Electrical Specifications – DC and AC

46

Rev.2.0 June 2016

© 2015 Alliance Memory, Inc. All rights reserved.

Alliance Memory Inc. reserves the right to change products or specification without notice

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070

TEL: (650) 610-6800 FAX: (650) 620-9211