Datasheet

Table Of Contents

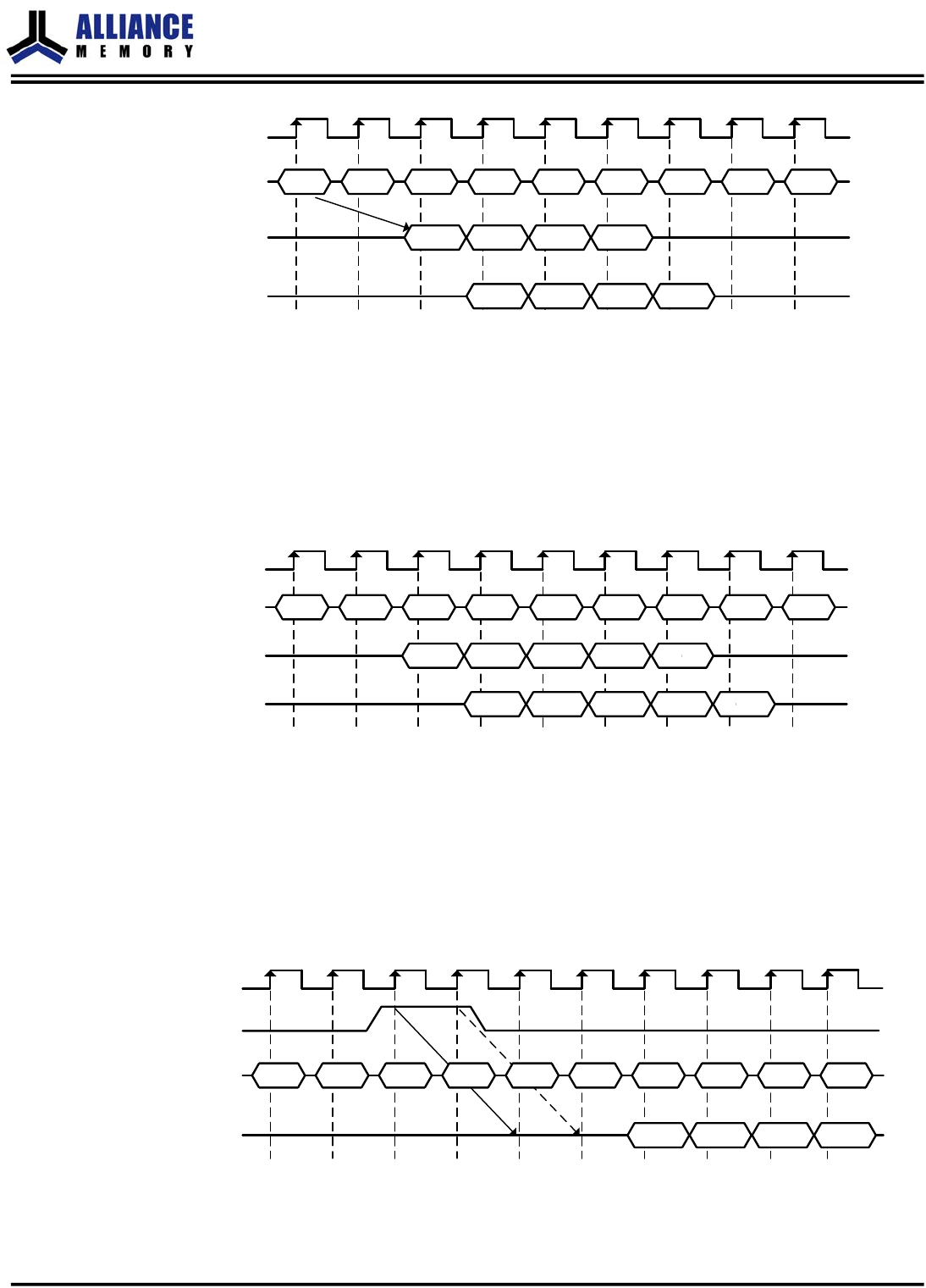

CLK

COMMAND

T0

T1 T2 T3 T4 T5 T6

READ A NOP NOP NOP NOP NOP NOP NOP

T7 T8

NOP

CAS# Latency=2

t

CK2

, DQ

CAS# Latency=3

t

CK3

, DQ

DOUT A

0

DOUT A

1

DOUT A

2

DOUT A

3

DOUT A

0

DOUT A

1

DOUT A

2

DOUT A

3

Figure 4. Burst Read Operation

(Burst Length = 4, CAS# Latency = 2, 3)

The read data appears on the DQs subject to the values on the DQM inputs two clocks earlier (i.e. DQM

latency is two clocks for output buffers). A read burst without the auto precharge function may be

interrupted by a subsequent Read or Write command to the same bank or the other active bank before

the end of the burst length. It may be interrupted by a BankPrecharge/ PrechargeAll command to the

same bank too. The interrupt coming from the Read command can occur on any clock cycle following a

previous Read command (refer to the following figure).

CLK

COMMAND

T0

T1 T2 T3 T4 T5 T6

READ A READ B NOP NOP NOP NOP NOP NOP

T7 T8

NOP

CAS# Latency=2

t

CK2

, DQ

CAS# Latency=3

t

CK3

, DQ

DOUT A

0

DOUT B

0

DOUT B

1

DOUT B

2

DOUT A

0

DOUT B

0

DOUT B

1

DOUT B

2

DOUT B

3

DOUT B

3

Figure 5. Read Interrupted by a Read

(Burst Length = 4, CAS# Latency = 2, 3)

The DQM inputs are used to avoid I/O contention on the DQ pins when the interrupt comes from a Write

command. The DQMs must be asserted (HIGH) at least two clocks prior to the Write command to

suppress data-out on the DQ pins. To guarantee the DQ pins against I/O contention, a single cycle with

high-impedance on the DQ pins must occur between the last read data and the Write command (refer to

the following three figures). If the data output of the burst read occurs at the second clock of the burst

write, the DQMs must be asserted (HIGH) at least one clock prior to the Write command to avoid internal

bus contention.

CLK

COMMAND

T0

T1 T2 T3 T4 T5 T6

NOP NOP

Bank A

Activate

NOP NOP READ A WRITE A NOP

T7 T8

NOP

CAS# Latency=2

t

CK2

, DQ

DQM

T9

NOP

DIN A

0

DIN A

1

DIN A

2

DIN A

3

Figure 6. Read to Write Interval

(Burst Length 4, CAS# Latency = 2)

AS4C4M16SA-C&I

Confidential

- 9 of 56 -

Rev.5.0 October 2018