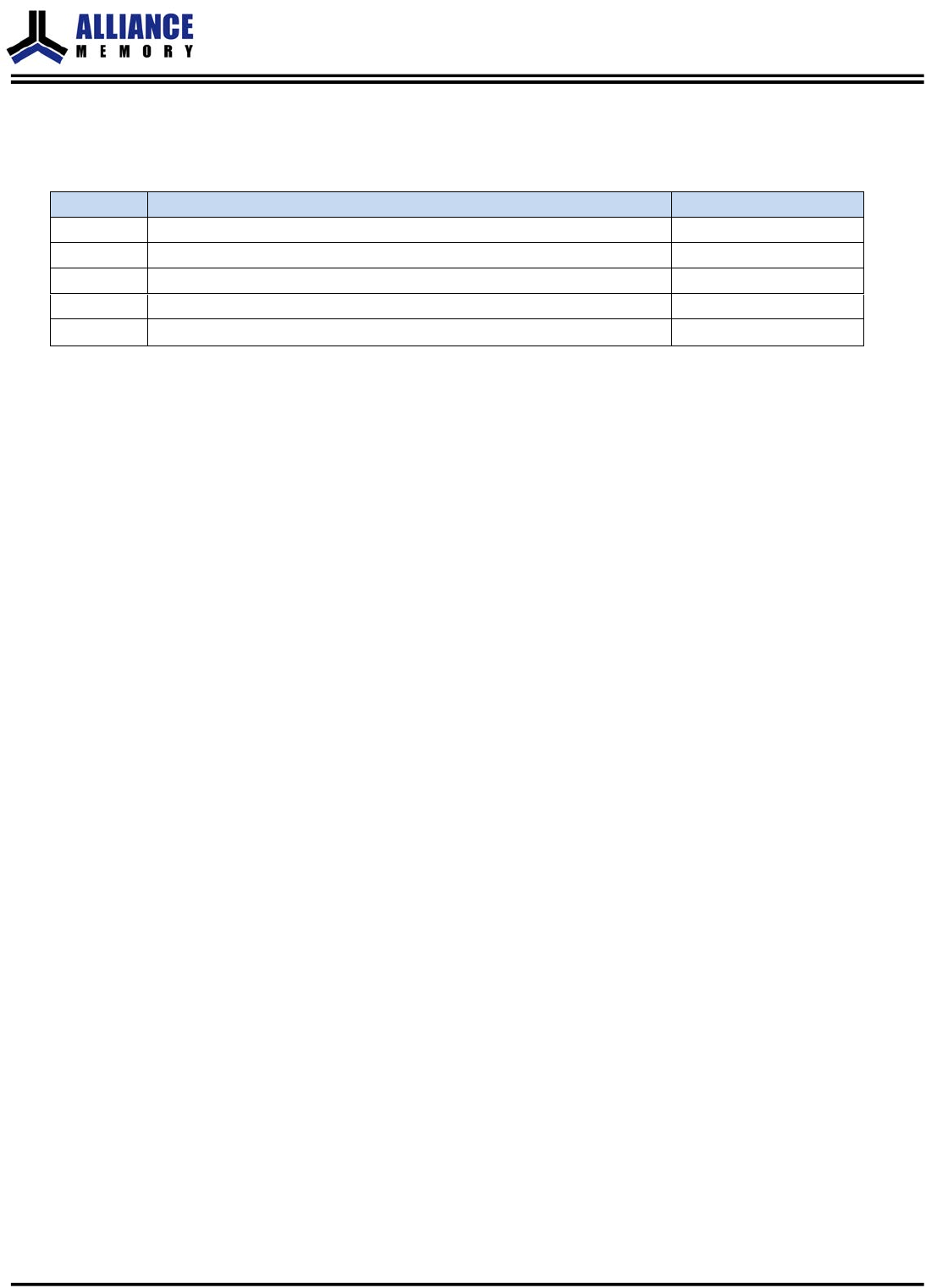

AS4C4M16SA-C&I Revision History Revision Rev 1.0 Rev 2.0 Rev 3.0 Rev 4.0 Rev 5.0 Details Preliminary datasheet. Modify some typing errors. Add AS4C4M16SA-6TCN part. Add AS4C4M16SA-7B2CN 60-ball package and Part Number. Add AS4C4M16SA-5TCN 54-Pin TSOPII and Part Number. Date June 2013 March 2014 March 2015 March 2017 October 2018 Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 610-6800 FAX: (650) 620-9211 Alliance Memory Inc.

AS4C4M16SA-C&I Confidential 64M – (4M x 16 bit) Synchronous DRAM (SDRAM) Advanced (Rev. 5.0, Oct. /2018) Features Overview Fast access time from clock: 4.5/5.4/5.

AS4C4M16SA-C&I Figure 1.2 54 Ball Assignment (Top View) Figure 1.

AS4C4M16SA-C&I Figure 2.

AS4C4M16SA-C&I Pin Descriptions Table 3. Pin Details Symbol Type Description CLK Input Clock: CLK is driven by the system clock. All SDRAM input signals are sampled on the positive edge of CLK. CLK also increments the internal burst counter and controls the output registers. CKE Input Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CLK signal.

AS4C4M16SA-C&I LDQM, UDQM Input DQ0-DQ15 Input / Output NC/RFU - VDDQ Supply Data Input/Output Mask: Controls output buffers in read mode and masks Input data in write mode. Data I/O: The DQ0-15 input and output data are synchronized with the positive edges of CLK. The I/Os are maskable during Reads and Writes. No Connect: These pins should be left unconnected. DQ Power: Provide isolated power to DQs for improved noise immunity. ( 3.3V 0.

AS4C4M16SA-C&I Operation Mode Fully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 4 shows the truth table for the operation commands. Table 4.

AS4C4M16SA-C&I Commands 1 BankActivate (RAS# = "L", CAS# = "H", WE# = "H", BAs = Bank, A0-A11 = Row Address) The BankActivate command activates the idle bank designated by the BA0, 1 signal. By latching the row address on A0 to A11 at the time of this command, the selected row access is initiated. The read or write operation in the same bank can occur after a time delay of tRCD(min.) from the time of bank activation.

AS4C4M16SA-C&I T1 T0 T2 T3 T4 T5 T6 T7 T8 CLK COMMAND READ A NOP NOP CAS# Latency=2 tCK2, DQ DOUT A0 CAS# Latency=3 tCK3, DQ NOP NOP NOP NOP DOUT A1 DOUT A2 DOUT A3 DOUT A0 DOUT A1 DOUT A2 NOP NOP DOUT A3 Figure 4. Burst Read Operation (Burst Length = 4, CAS# Latency = 2, 3) The read data appears on the DQs subject to the values on the DQM inputs two clocks earlier (i.e. DQM latency is two clocks for output buffers).

AS4C4M16SA-C&I T1 T0 T2 T3 T4 T5 T6 T7 T8 CLK DQM COMMAND NOP READ A NOP NOP NOP CAS# Latency=3 tCK3, DQ NOP WRITE B NOP NOP DIN B0 DIN B1 DIN B2 DOUT A0 Must be Hi-Z before the Write Command Don’t Care Figure 7.

AS4C4M16SA-C&I 6 Write command (RAS# = "H", CAS# = "L", WE# = "L", BAs = Bank, A10 = "L", A0-A7 = Column Address) The Write command is used to write a burst of data on consecutive clock cycles from an active row in an active bank. The bank must be active for at least tRCD(min.) before the Write command is issued. During write bursts, the first valid data-in element will be registered coincident with the Write command.

AS4C4M16SA-C&I Figure 12. Write Interrupted by a Read (Burst Length = 4, CAS# Latency = 2, 3) The BankPrecharge/PrechargeAll command that interrupts a write burst without the auto precharge function should be issued m cycles after the clock edge in which the last data-in element is registered, where m equals tWR/tCK rounded up to the next whole number.

AS4C4M16SA-C&I Table 5.

AS4C4M16SA-C&I Burst Length Field (A2~A0) This field specifies the data length of column access using the A2~A0 pins and selects the Burst Length to be 2, 4, 8, or full page. Table 6. Burst Length Field A2 A1 A0 Burst Length 0 0 0 1 0 0 1 2 0 1 0 4 0 1 1 8 1 0 0 Reserved 1 0 1 Reserved 1 1 0 Reserved 1 1 1 Full Page Burst Type Field (A3) The Burst Type can be one of two modes, Interleave Mode or Sequential Mode. Table 7.

AS4C4M16SA-C&I CAS Latency Field (A6~A4) This field specifies the number of clock cycles from the assertion of the Read command to the first read whole value satisfying the following formula must be programmed into this field. tCAC(min) CAS Latency X tCK Table 9.

AS4C4M16SA-C&I 9 No-Operation command (RAS# = "H", CAS# = "H", WE# = "H") The No-Operation command is used to perform a NOP to the SDRAM which is selected (CS# is Low). This prevents unwanted commands from being registered during idle or wait states. 10 Burst Stop command (RAS# = "H", CAS# = "H", WE# = "L") The Burst Stop command is used to terminate either fixed-length or full-page bursts. This command is only effective in a read/write burst without the auto precharge function.

AS4C4M16SA-C&I 13 SelfRefresh Entry command (RAS# = "L", CAS# = "L", WE# = "H", CKE = "L", A0-A11 = Don't care) The SelfRefresh is another refresh mode available in the SDRAM. It is the preferred refresh mode for data retention and low power operation. Once the SelfRefresh command is registered, all the inputs to the SDRAM become "don't care" with the exception of CKE, which must remain LOW. The refresh addressing and timing is internally generated to reduce power consumption.

AS4C4M16SA-C&I Table 13. Absolute Maximum Rating Symbol Item - 5/6/7 Unit Note VIN, VOUT Input, Output Voltage - 1.0 ~ 4.6 V 1 VDD, VDDQ Power Supply Voltage -1.0 ~ 4.6 V 1 Commercial 0 ~ 70 °C 1 Industrial -40 ~ 85 °C 1 TA Ambient Temperature TSTG Storage Temperature - 55 ~ 150 °C 1 PD Power Dissipation 1 W 1 IOS Short Circuit Output Current 50 mA 1 Table 14. Recommended D.C. Operating Conditions (TA = -40~85°C) Symbol Parameter Min. Typ. Max.

AS4C4M16SA-C&I Table 16. D.C. Characteristics (VDD = 3.3V 0.

AS4C4M16SA-C&I Table 17. Electrical Characteristics and Recommended A.C. Operating Conditions (VDD = 3.3V±0.3V, TA = -40~85°C) Symbol -5 A.C. Parameter -6 -7 Min. Max. Min. Max. Min. Max.

AS4C4M16SA-C&I Table 18. LVTTL Interface Reference Level of Output Signals 1.4V / 1.4V Output Load Reference to the Under Output Load (B) Input Signal Levels 2.4V / 0.4V Transition Time (Rise and Fall) of Input Signals 1ns Reference Level of Input Signals 1.4V 1.4V 3.3V 50Ω 1.2KΩ Output Output 30pF 870Ω Figure 18.1 LVTTL D.C. Test Load (A) Z0=50Ω 30pF Figure 18.2 LVTTL A.C. Test Load (B) 7. Transition times are measured between VIH and VIL.

AS4C4M16SA-C&I Timing Waveforms Figure 19.

AS4C4M16SA-C&I Figure 20.

AS4C4M16SA-C&I Figure 21. Auto Refresh (Burst Length=4, CAS# Latency=2) T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK CKE CS# RAS# CAS# WE# BA0,1 A10 RAx A0-A9, A11 RAx tRP tRC tRC CAx tRCD DQM DQ Ax0 Precharge All Command Auto Refresh Command Auto Refresh Command Activate Command Bank A Ax1 Read Command Bank A Don’t Care Confidential - 24 of 56 - Rev.5.

AS4C4M16SA-C&I Figure 22.

AS4C4M16SA-C&I Figure 23. Self Refresh Entry & Exit Cycle T0 T1 T2 T3 T4 CLK *Note 1 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 *Note 2 CKE CS# T5 T6 tXSR *Note 5 *Note 3,4 tIS tIH *Note 6 tIS *Note 8 tPDE *Note 7 RAS# *Note 9 CAS# WE# BA0,1 A10 A0-A9, A11 DQM DQ Hi-Z Hi-Z Self Refresh Exit Self Refresh Entry Auto Refresh Don’t Care Note: To Enter SelfRefresh Mode 1. CS#, RAS# & CAS# with CKE should be low at the same clock cycle. 2.

AS4C4M16SA-C&I Figure 24.1. Clock Suspension During Burst Read (Using CKE) (Burst Length=4, CAS# Latency=2) T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK CKE CS# RAS# CAS# WE# BA0,1 A10 RAx A0-A9, A11 RAx CAx DQM DQ tHZ Hi-Z Ax0 Activate Command Bank A Read Command Bank A Ax1 Ax2 Clock Suspend 1 Cycle Clock Suspend 2 Cycles Ax3 Clock Suspend 3 Cycles Don’t Care Confidential - 27 of 56 - Rev.5.

AS4C4M16SA-C&I Figure 24.2. Clock Suspension During Burst Read (Using CKE) (Burst Length=4, CAS# Latency=3) T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK CKE CS# RAS# CAS# WE# BA0,1 A10 RAx A0-A9, A11 RAx CAx DQM DQ tHZ Hi-Z Ax0 Activate Command Bank A Read Command Bank A Ax1 Clock Suspend 1 Cycle Ax2 Clock Suspend 2 Cycles Ax3 Clock Suspend 3 Cycles Don’t Care Confidential - 28 of 56 - Rev.5.

AS4C4M16SA-C&I Figure 25. Clock Suspension During Burst Write (Using CKE) (Burst Length=4) T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK CKE CS# RAS# CAS# WE# BA0,1 A10 RAx A0-A9, A11 RAx CAx DQM DQ Hi-Z DAx0 Activate Command Bank A Confidential DAx1 Clock Suspend 1 Cycle Write Command Bank A DAx2 Clock Suspend 2 Cycles DAx3 Clock Suspend 3 Cycles Don’t Care - 29 of 56 - Rev.5.

AS4C4M16SA-C&I Figure 26.

AS4C4M16SA-C&I Figure 27.1.

AS4C4M16SA-C&I Figure 27.2.

AS4C4M16SA-C&I Figure 28.

AS4C4M16SA-C&I Figure 29.1.

AS4C4M16SA-C&I Figure 29.2.

AS4C4M16SA-C&I Figure 30.

AS4C4M16SA-C&I Figure 31.1.

AS4C4M16SA-C&I Figure 31.2.

AS4C4M16SA-C&I Figure 32.1.

AS4C4M16SA-C&I Figure 32.2.

AS4C4M16SA-C&I Figure 33.

AS4C4M16SA-C&I Figure 34.1.

AS4C4M16SA-C&I Figure 34.2.

AS4C4M16SA-C&I Figure 35.

AS4C4M16SA-C&I Figure 36.1.

AS4C4M16SA-C&I Figure 36.2.

AS4C4M16SA-C&I Figure 37.

AS4C4M16SA-C&I Figure 38.

AS4C4M16SA-C&I Figure 39.

AS4C4M16SA-C&I Figure 40.

AS4C4M16SA-C&I Figure 41 Full Page Random Column Write (Burst Length=Full Page) T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK CKE CS# RAS# CAS# WE# BA0,1 A10 RAx RBx A0-A9, A11 RAx RBx RBw CAx CBx CBy CAy CAz CBz RBw tWR tRP DQM DQ Hi-Z tRRD DAx0 DAx1 Activate Command Bank A Confidential tRCD Activate Command Bank B Write Command Bank A DBx0 DAy0 DAy1 DBy0 DBy1 Write Command Bank B Write Command Bank A Write Command Bank B DAz0 DAz1 W

AS4C4M16SA-C&I Figure 42 Precharge Termination of a Burst (Burst Length=4, 8 or Full Page, CAS# Latency=3) T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK CKE High CS# RAS# CAS# WE# BA0,1 A10 RAx A0-A9, A11 RAx RAy CAx RAy tWR RAz CAy RAz tRP tRP DQM DQ DAx0 DAx1 Activate Command Bank B Confidential Precharge Write Command Command Bank A Bank A Precharge Termination of a Write Burst Write Data are masked Ay0 Activate Command Bank A Read Comman

AS4C4M16SA-C&I Figure 43. 54 Pin TSOP II Package Outline Drawing Information Symbol A A1 A2 B C D E e HE L L1 S y θ Min Dimension in inch Nom Max --0.002 0.035 0.01 0.004 0.87 0.395 --0.455 0.016 ----0° ----0.039 0.014 0.006 0.875 0.400 0.031 0.463 0.02 0.032 0.028 ----- 0.047 0.008 0.043 0.018 0.008 0.88 0.405 --0.471 0.024 ----0.004 8° Min Dimension in mm Nom Max --0.05 0.9 0.25 0.12 22.09 10.03 --11.56 0.4 ------0° ----1.0 0.35 0.165 22.22 10.16 0.8 11.76 0.5 0.84 0.71 ----- 1.2 0.2 1.1 0.

AS4C4M16SA-C&I Figure 44. 54 Ball TFBGA Package Outline Drawing Information A1 INDEX Bottom View TOP View Side View Symbol A A1 A2 D E D1 E1 e b F Confidential Dimension in inch Min Nom Max --0.047 0.010 0.012 0.014 -0.033 -0.311 0.315 0.319 0.311 0.315 0.319 -0.252 --0.252 --0.031 -0.016 0.018 0.020 -0.126 -- - 54 of 56 - Dimension in mm Min Nom Max --1.20 0.25 0.30 0.35 -0.85 -7.90 8.00 8.10 7.90 8.00 8.10 -6.40 --6.40 --0.80 -0.40 0.45 0.50 -3.20 -- Rev.5.

AS4C4M16SA-C&I Figure 45. VFBGA 60ball Package Outline Drawing Information Symbol A A1 A2 c D E D1 E1 e b F Confidential Dimension in inch Min Nom Max --0.039 0.008 0.010 0.120 0.024 0.026 0.028 0.007 0.008 0.010 0.248 0.252 0.256 0.394 0.398 0.402 -0.154 --0.358 --0.026 -0.012 0.014 0.016 -0.102 -- - 55 of 56 - Dimension in mm Min Nom Max --1.00 0.20 0.25 0.30 0.61 0.66 0.71 0.17 0.21 0.25 6.30 6.40 6.50 10.00 10.10 10.20 -3.90 --9.10 --0.65 -0.30 0.35 0.40 -2.60 -- Rev.5.

AS4C4M16SA-C&I PART NUMBERING SYSTEM AS4C DRAM 4M16SA 4M16=4Mx16 S=SDRAM A=A die version 5/6/7 5=200MHz 6=166MHz 7=143MHz T/B/B2 C/I N XX C=Commercial T = TSOP II Indicates Pb Packing Type (0° C~70° C) B = 54ball FBGA and Halogen None:Tray I=Industrial Free B2 = 60ball FBGA TR:Reel (-40° C~85° C) Alliance Memory, Inc. 511 Taylor Way, San Carlos, CA 94070 Tel: 650-610-6800 Fax: 650-620-9211 www.alliancememory.com Copyright © Alliance Memory All Rights Reserved © Copyright 2007 Alliance Memory, Inc.