Technical data

Table Of Contents

6 IEEE-488.2 Common Commands

44 U2751A Programmer’s Reference Guide

*STB?

Syntax

*STB?

Queries the condition register for the Status Byte register group. The bits

are not cleared when you read the register.

Remarks

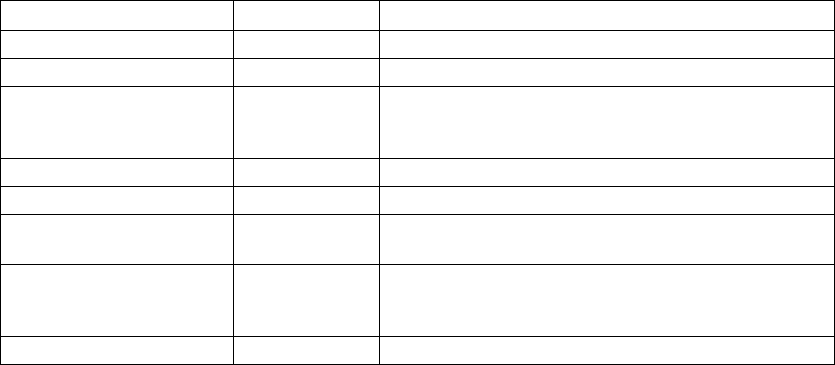

• The following table lists the bit definitions for the Status Byte register.

• The Status Byte condition register is cleared when you execute the

clear status (*CLS) command. Clearing an event register will clear the

corresponding bits in the Status Byte summary register (bit 5).

• The Status Byte Enable register is cleared when you execute the

*SRE 0 command.

Bit number Decimal value Definition

0 Not Used 1 Always zero.

1 Not Used 2 Always zero.

2 Error Queue 4 There is at least one error code in the error queue. Use the

SYSTem:ERRor? command to read and clear the error from the

queue.

3 Not Used 8 Always zero.

4 Message Available 16 Data is available in the instrument's output buffer.

5 Standard Event 32 One or more bits are set in the Standard Event register (bits

must be enabled, refer to the *ESE command).

6 Master Summary 64 One or more bits are set in the Status Byte register and may

generate a Request for Service (RQS). Bits must be enabled

using the *SRE command.

7 Not Used 128 Always zero.